Hi team:

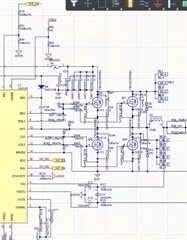

My customer using LM5143 and found some funny issues.

1. 48Vin, 24V(Channel2) & 10Vout

2. If the Enable signal takes precedence over Vin, Channel 2 of 24V will becomes 5V. and seems go into protection mode? Channel 1 of 10V works well.

Green : EN

Blue: Vin

Purple: 24Voutput

Tks for your checking.