Hi,

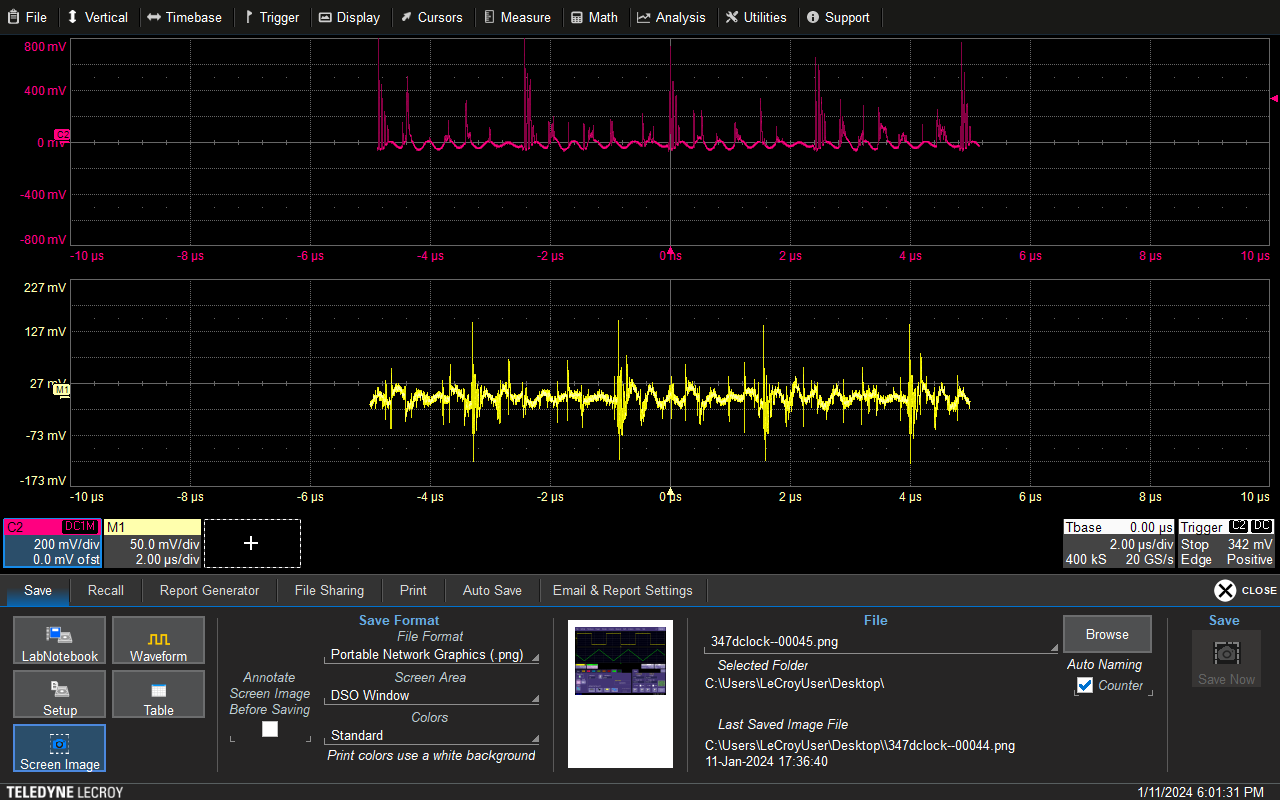

I have got reviewed the schematic and layout here

TPS63710: TPS63710 Layout Review - Power management forum - Power management - TI E2E support forums

Now i have got the realised board in my hand

What i am observing is quite strange after a minute of time the power ic keeps on restarting and the output voltage is not stable as the output is off for a while, kindly let me know where exactly the problem might be wrong with my schematic ?

i am reposting the schemati again below

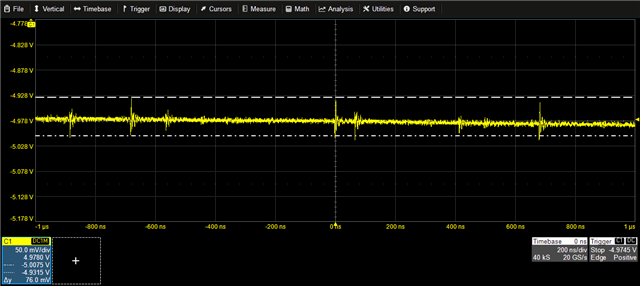

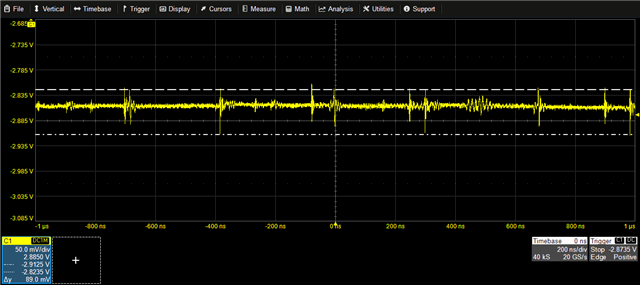

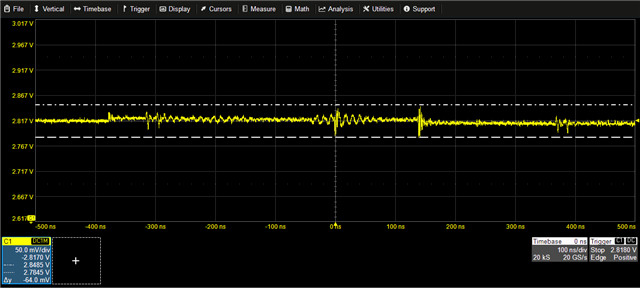

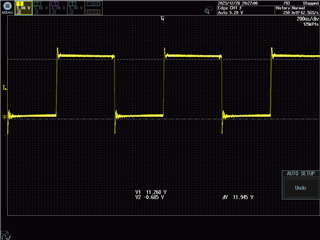

The wavefrom of SW is as below

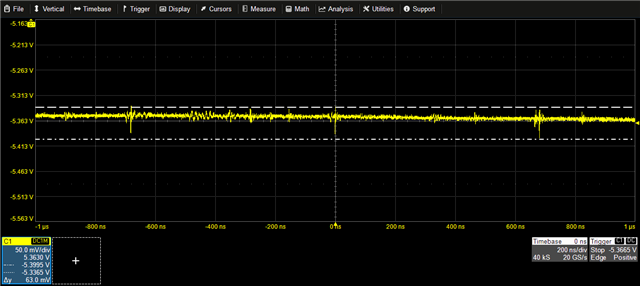

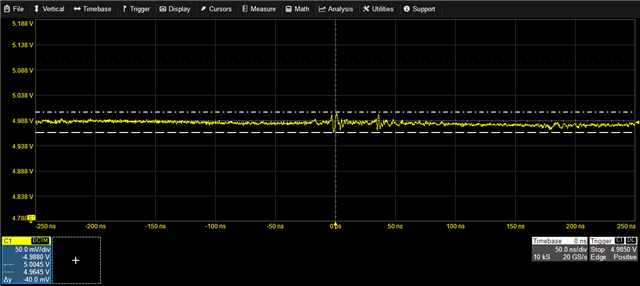

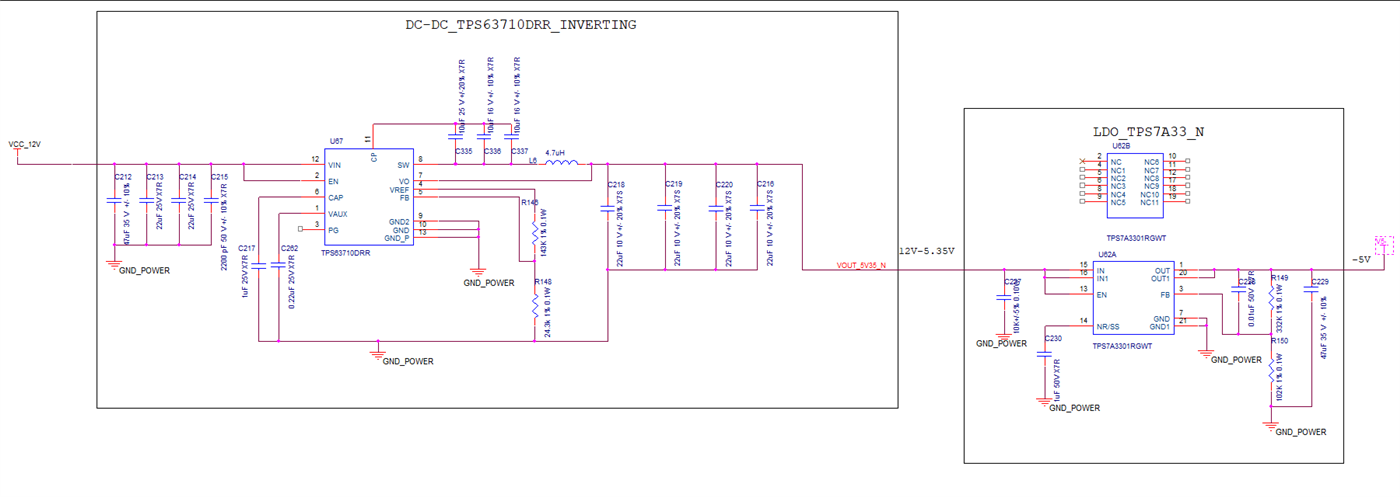

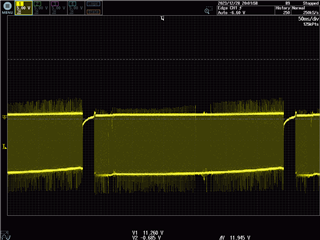

Waveform of CP is as below

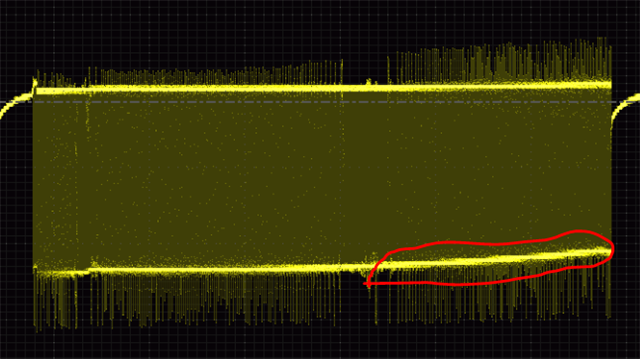

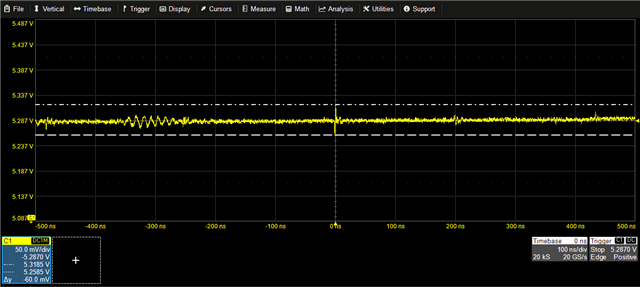

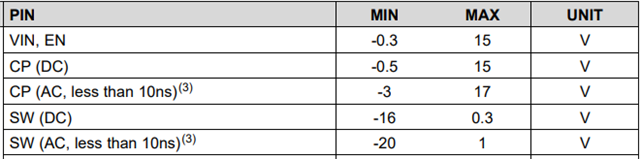

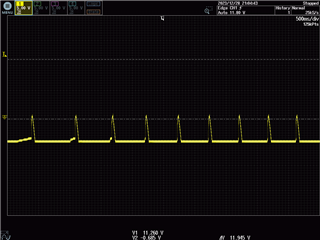

After a minute of time i observe the waveform like below in long time-scale which is a clear indication of restart of regualtor and there by heating the board so much

1. Suspecting C219 and C220, i have removed the extra 22uF Capacitance

2. C215 is also removed as its wrongly put with small value

Still the output remains the same at SW

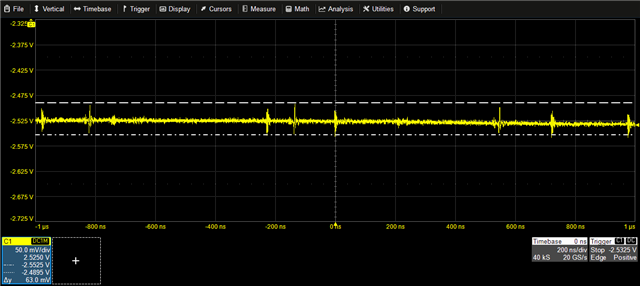

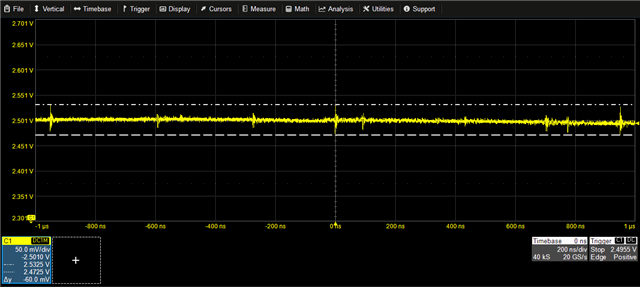

eventually the output at DCDC is as below

Is there anything wrong in the schematic which is creating this issue, kindly help

NOTE : a similar approach i have used for creating -2.85 followed by LDO to create -2.5V in which there is no issue, but this higher negative voltage is creating the issue.