Other Parts Discussed in Thread: LM3478,

Hi Niklas,

I have a couple of questions, I am going for a 4.7uf cap on SS pin to get a soft start of 500msec.

- Is there any max capacitance limit on SS pin ?

- Will this affect the RT pin bias resistor value or COMP pin network ?

- What is the value of fRT (typical) ?

- Would it be better to go with the high switching frequency with 500msec of soft start ?

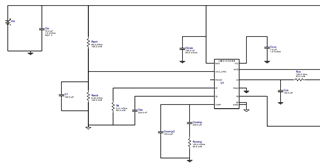

Attached is the snap of Webench design that I have currently.

Please let me know.

Thanks..!!!