Other Parts Discussed in Thread: LM7481

Hello, we are planning to use the LM7481 on an interface that could be hot-plugged by a live voltage source. Given this we need to mitigate the inrush due to input capacitance.

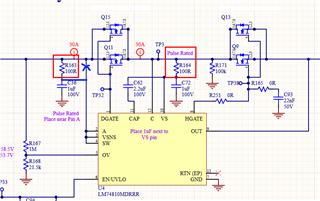

We would like to use 100ohm resistors in series with the capacitance that is connected to Pin 2 (A), Pin 11 (CAP), and Pin 10 (VS), to limit inrush as without them it would be several amps into the capacitor.

Is there an issue with having a 100ohm series resistor (R164) in line to the CAP and VS pins as shown in the below schematic?

Would there be an issue if we have a 100ohm (R163) in line with the Anode connection? (if we were to modify circuit with blue connections shown below) My concern was pins A and C are used for accurate reverse current protection, so additional resistance might affect the accuracy of that protection depending on how that stage is designed internal to the chip?

Thank you,

Peter Davis