Other Parts Discussed in Thread: , UCC2895

Hello,

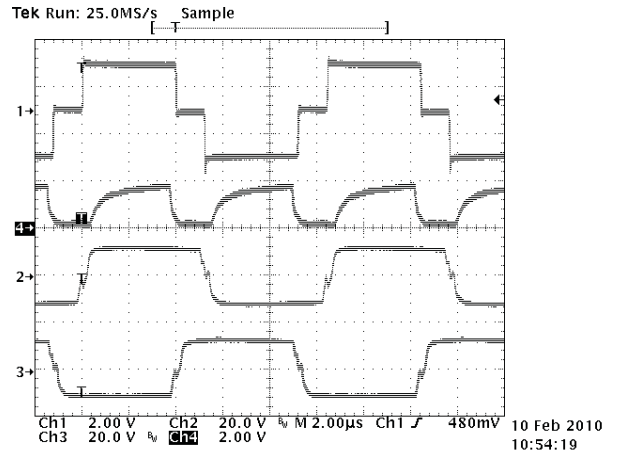

The waveform in Fig1 can be seen every few times during burst mode under light load.

What is this happening?

I usually use Fig2 most of the time.

Is this normal? Are there any countermeasures?

I'm working on increasing the efficiency of light loads.

I think it would be even better if this was removed.

regards

Wave form_Light Load.pdf