Other Parts Discussed in Thread: LM317, LMR36510

Hello,

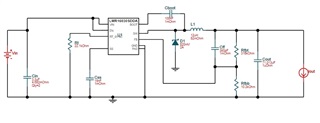

It seems odd that the algorithm to buck +48v down to +24v produced odd component values. Such as the schematic output capacitor is very low (100nF) and 3mΩ FB circuit and BOM used huge 0603 resistors that are not in the NFET switching path, why? The choices that came up for low parts count selection and wide input voltage range for web page to ever show LMR16030 required buck 54v MAX 24v/3A, some selections had over 27 passives though less than 4 is more typical of other bucks, Web bench shows 11 piece BOM. Reference datasheet (SNVSAH9B – DECEMBER 2015 – REVISED MARCH 2021)

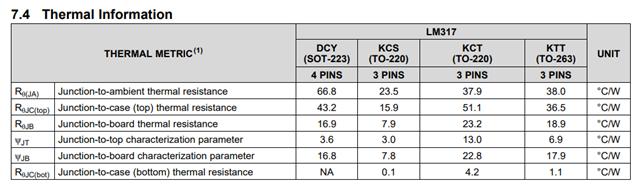

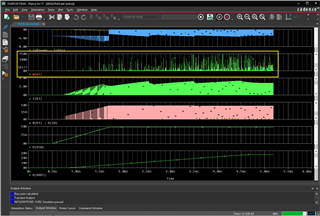

The battery input range +36v - +56v absolute max. Desiging for 48v LiFePo or SLA battery to float 52v max ever rebalancing discussed some forums some batteries refuse to charge though many cycles being left. The actual host PCB current is <1A powered by linear 24v DC supply LM317. The PCB sports 3 Rohm bucks absolute 45v input, hence the reason to update design to handle 48v variable input range. Could you please point me to any other bucks that have fewer passives perhaps specifically designed to handle variable +48v battery source? Why does the schematic for Tina export have only 100nF to hold down switching ripple? The 3 bucks (+5,+12,+15v) have 22µF ceramic each and one or several distant 22µF bulk electrolytics near current source points. The 3 bucks switch 1.5MHz in 20-40KHZ PWM inductive drive system. Each buck has 9-piece BOM with one EN detect threshold circuit for +5v, +15v, hence SS feature LMR was chosen. The current inductors are 10µH keeping BOM light so LMR 22µH with 1nF output filter seems way off even for 500KHz switching.

Web Bench exported zip:

Thanks for any answers or other devices to meet the requirement!