Hi,

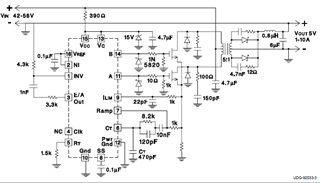

I'm working on a flyback design using a legacy part, UC1825BJ/883B, and I've encountered some technical concerns that I hope you could shed some light on.

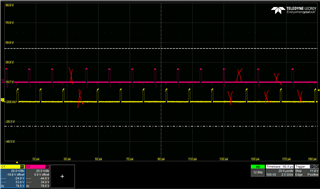

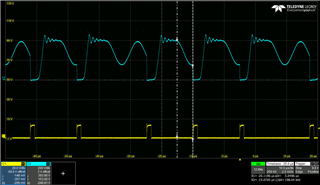

The issue I'm facing is that OUTPUTA and OUTPUTB often miss a cycle under the same load conditions. OUTPUT_A is tied to the gate of a MOSFET, while OUTPUT_B is left open. I've already verified that ILIM stays below the Current Limit/OverCurrent threshold.

Channel#1: OUTA | Channel#2: OUTB |Channel#3: CLK

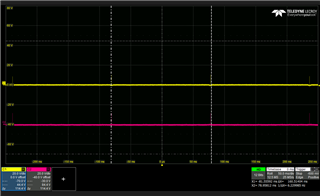

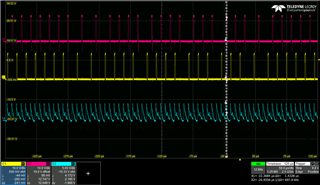

CH1: OUTA, CH3: V_DS on the MOSFET

Wondering if you have any suggestion where I should look into regarding this cycle skipping issue/feature. Which portion of the part/circuit might control this valley detection/ Somewhat Zero Voltage Switching on VDS?