Hi everyone,

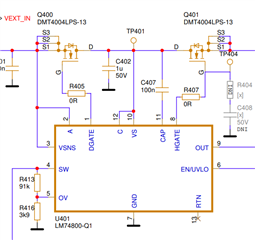

I'm using the LM7480-Q1 in my schematic as an Ideal Diode IC and an Input Source Selection circuitry between two input sources. However, while testing the IC (only one channel, not changing betweem the two input sources), I just noticed a strange behaviour. The IC is working fine as soon as the EN/UVLO pin is pulled high (3.3V), but when I try to disable it (pulling EN/UVLO low at 0V) the DGATE and HGATE driver signals remain high! I have tested it with my two input sources independently, and I experienced difference behaviours as well even though the circuits are the same:

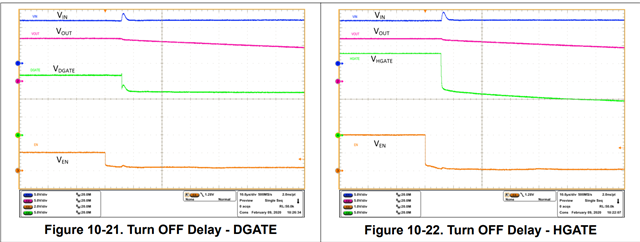

- 24V input source: the DGATE signal is still high when the EN/UVLO pin is pulled low (0V), but the HGATE signal is pulled low (which should also happen to the DGATE signal).

- Battery input source (around 23V): both DGATE and HGATE signals are still high when the EN/UVLO pin is pulled low (0V).

I checked it and the EN/UVLO voltage is exactly 0.0V in both cases to check that it's below the minimum V(ENF) voltage (0.3V according to the datasheet). In this case, the LM7480-Q1 should enter shutdown mode, disabling both gate drivers, but apparently it's not working as intended. Below you can find the schematic for the 24V input source (as an example):

In this case, the R404 and C408 are mounted to reduce the inrush current (100Ohms and 22nF, respectively).

I hope this is enough information for you to help me determine the source of the issue. Thank you very much for your time and I'm looking forward to your reply.

Best regards,

Juan