Hi Ti Team,

I have used multiple TPS568230RJER devices in our projects.

We are facing couple of issues with this module, please go through the following problem statement-

Problem- 1: Regulator's output voltage ramps even if Enable is not provided.

Actually, we are deriving FPGA's supply like (1V, 1.8V, 1.5V, 3,3V, etc) using the same device (TPS568230RJER). Enable and power goods of these devices are connected to implement the desired power sequencing.

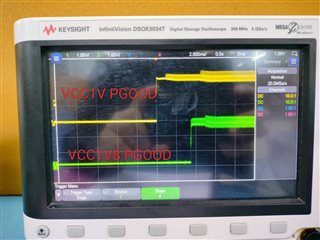

Here we will talk about only the 3.3V regulator whose enable pin is driven by power good of 1.8V regulator. But, This 3.3V regulator's output voltage starts ramping around 40-60ms before getting its enable signals from 1.8V regulator. this ramp voltage reaches up to 0.9V from 0V during this 40-60ms duration.

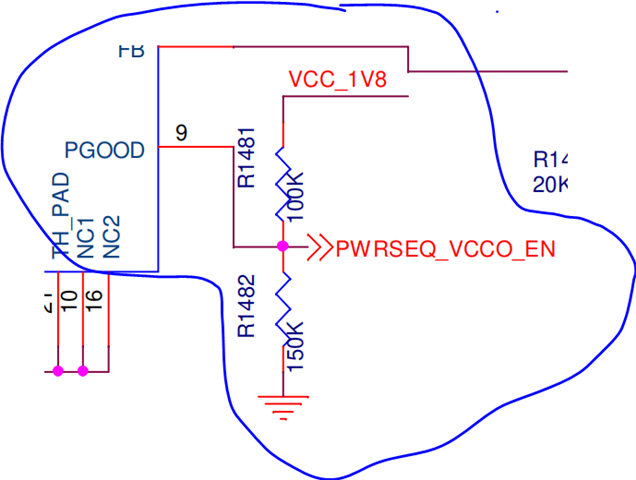

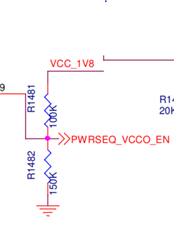

for your reference, please find the snaps of corresponding schematic-

As Enable pin doesn't take voltage above 3.6V so voltage divider circuit is applied on power good of 1.8V (between VCC and ground).

3V3 regulator's output waveform can be seen in the following image-

Problem-2: When I probed the VCC pin of the regulator which is ouput pin of internal LDO. I observed the ripples, please refer the following image-

Please look into this as soon as possible, as we are facing the issue in debugging and the same part number is used for other ongoing projects also.

Thank You

Raj Kumar