Other Parts Discussed in Thread: AM3352, TPS65218, TPS6521815

Dear TI Expert Team,

I am writing to seek clarification about the bit 0 of INT2 register in TPS65216.

This bit is described as a "Reserved" in the datasheet.

We are currently evaluating engineering prototypes of a custom-designed board that utilizes AM3352 and TPS65216.

And we have encountered an issue where Linux does not boot up properly on one of these prototype boards.

The occurrence rate of this issue is approximately 30%, with the board sometimes booting up correctly and other times not.

None of the other prototype boards exhibit this problem, but we need to determine whether this issue is due to a design flaw or a defect in the individual component.

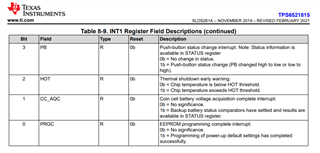

We've noticed differences in the INT1 and INT2 register values between successful and unsuccessful boot attempts. The values are as follows.

Successful Boot:

INT1 = 1 0, INT2 = 0 0

Unsuccessful Boot:

INT1 = 0 0, INT2 = 0 1

We understand that the 4th bit of the INT1 register relates to the AC_DET status, and we will investigate this on our end.

However, could you provide insight into what the difference in the 0th bit of the INT2 register indicates?

Additionally, even in cases of unsuccessful boot, the DCDC1 to DCDC4 and LDO1 power outputs are functioning normally.

After performing the power-up sequence, these outputs are stably supplying power to the AM3352, that was confirmed by oscilloscope waveforms.

I would appreciate any advice or comment you may have.

Thank you for your support.

Best regards,

Sota Inoue