Hi team,

My customer has two questions regarding TPS3430, can you help advise?

1. In the datasheet, it shows that,

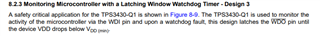

To achieve the latching watchdog feature, an open-drain buffer is connected from WDO to CRST with a small

value capacitor connected from the Anode of the buffer connected to CRST to GND.

Do you have recommended P/N for the buffer?

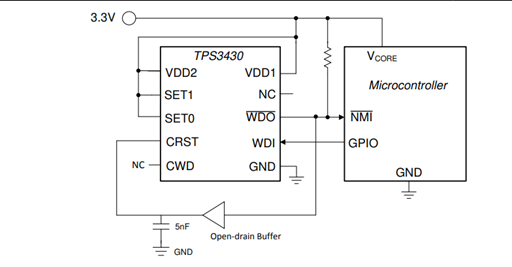

2. The second question is about Figure 8-10,

As shown in the figure below, when WDI has no input, WDO changes from high level to low level and remains in low level state until VDD is less than VDD(min). So if my VDD voltage is in a normal state, but WDI starts to feed normally after a long period of time, will WDO change from low level to high level? In other words, as long as WDI feeds the watchdog normally, then WDO will be at a high level. If WDI does not feed the watchdog, WDO will always be at a low level?

Regards,

Xiaoying