Hi all,

My product need PB with short press and long press function and 2 output power.

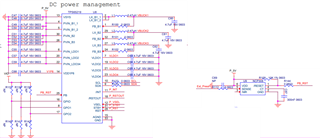

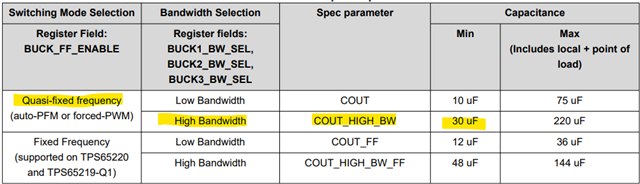

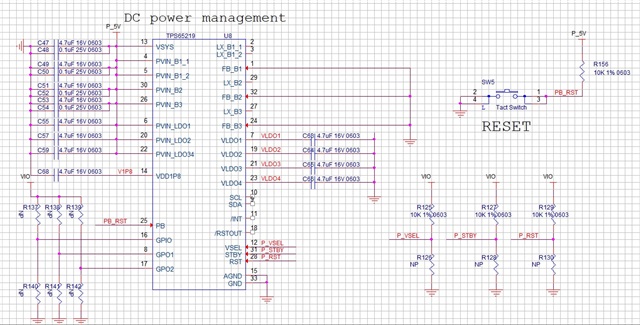

I select TPS6521902RHBR to fulfill my product.

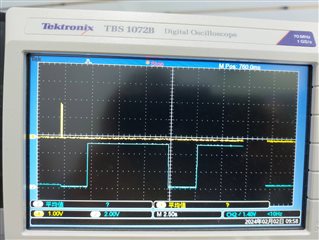

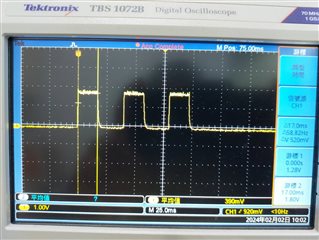

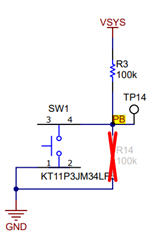

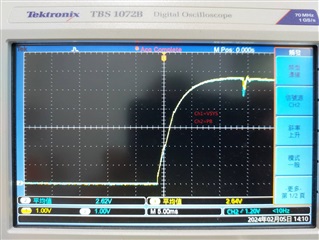

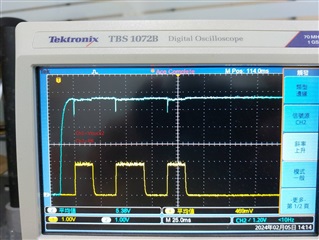

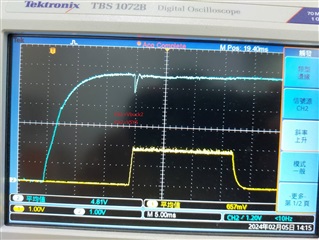

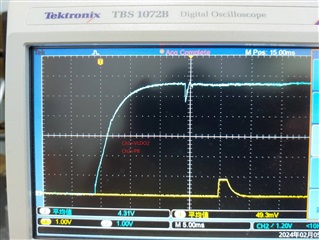

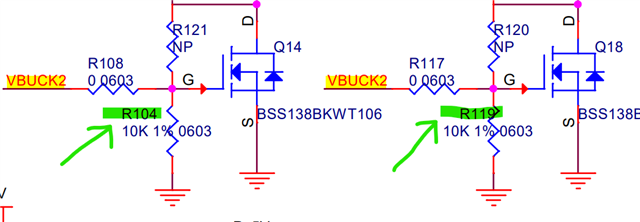

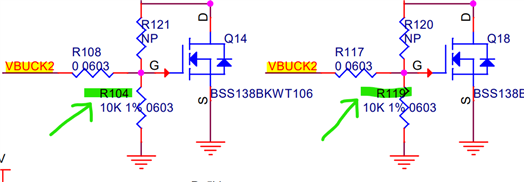

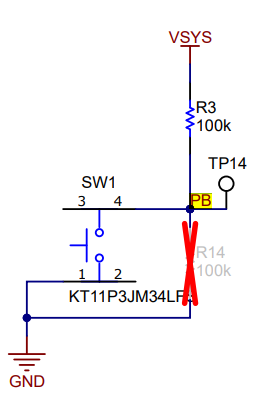

When I get ICs, in order to test "PB" function. Below is my test circuit.

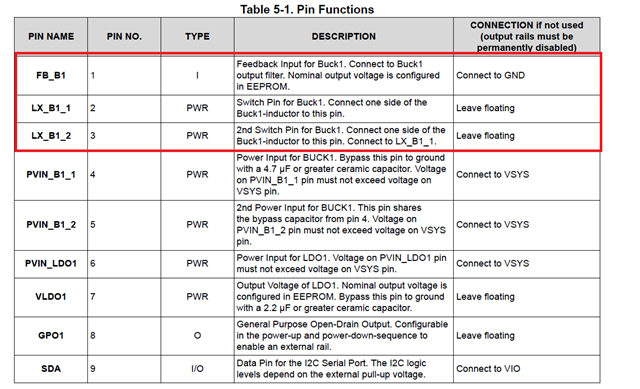

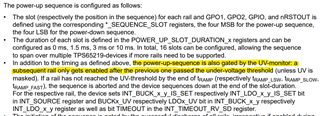

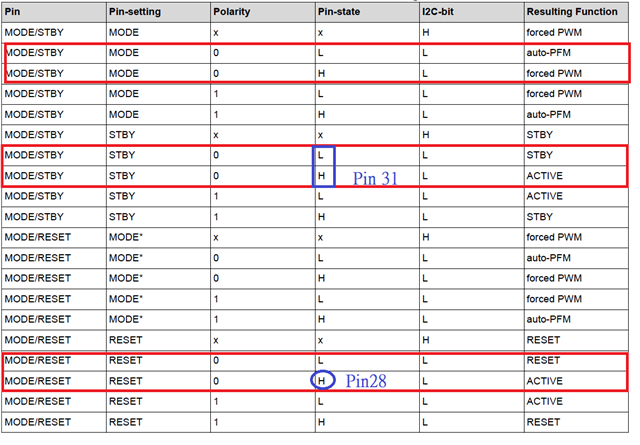

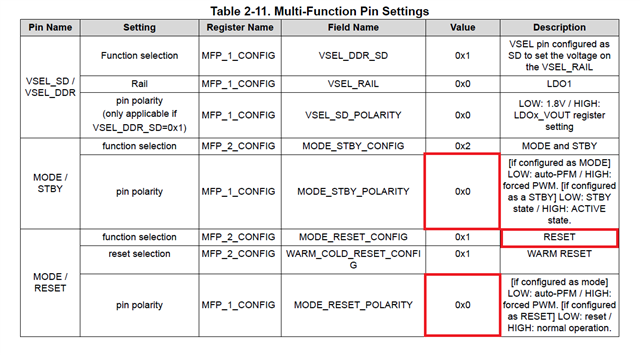

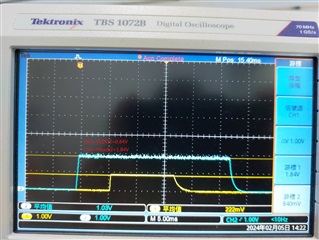

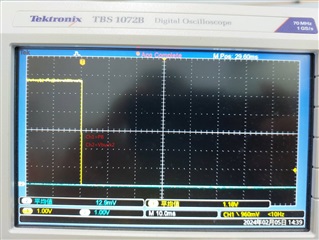

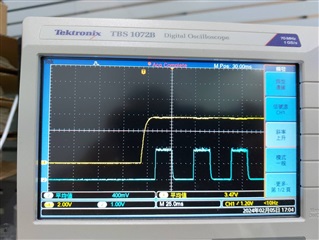

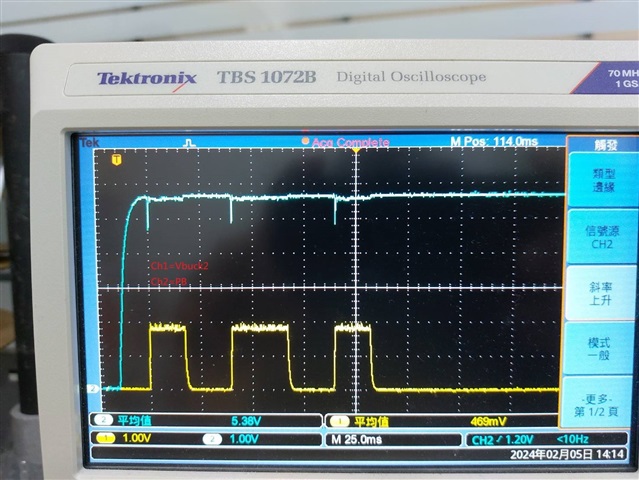

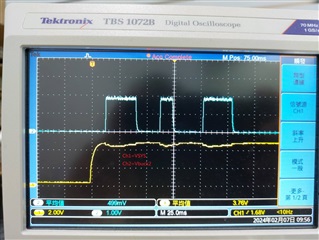

I try to use different kind of configure for VSEL/STBY/RST (pin12/pin31/pin28), but after press "PB" (pin25) still no output power.

Please help to help my questions as below:

Question 1: Plese help to checck if my circuit is NG or need to modify?

Question 2: Does TPS6521902RHBR need MCU to commuate to set output voltage?

Question 3 : Does TPS6521902RHBR can work normaly without MCU? How to do it?

Please provide help.

Thanks

Best Regarfds,

Eric