Hello!

I'm Takashi.

We are designing a power supply using UCC28064A.

Please tell us about the OCP operation of UCC28064A.

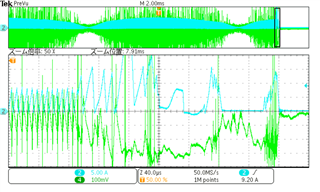

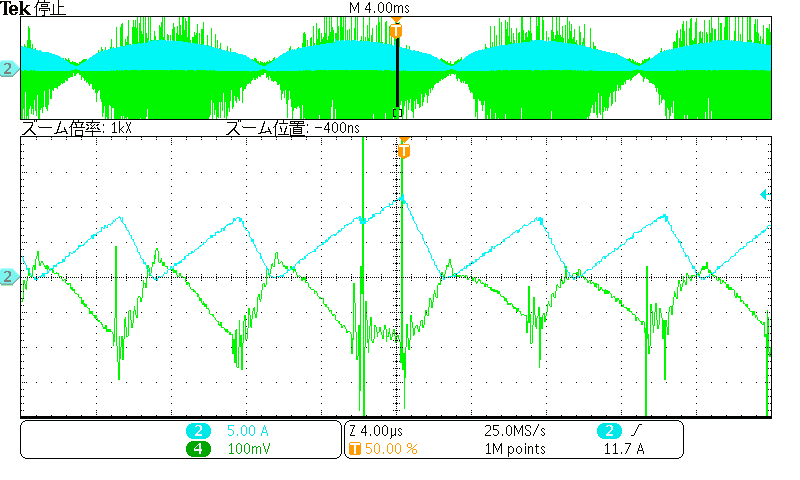

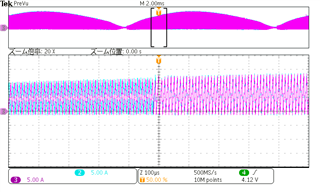

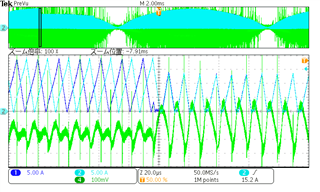

I will post the measured waveforms of the two-phase inductor current and CS terminal voltage when OCP operates.

ch1: Inductor current_B

ch2: Inductor current_A

ch4: CS terminal voltage

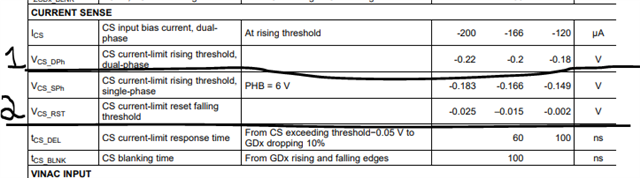

There are two things I want to know.

A) When OCP operates, the phases that were 180 degrees apart will overlap.

Is this behavior correct?

If this behavior is incorrect, please let me know how to fix it.

B) Current limiting by OCP starts in the middle of the sine wave.

Is this behavior correct?

If this behavior is incorrect, please let me know how to fix it.

Kind regards.