Other Parts Discussed in Thread: UCC21750,

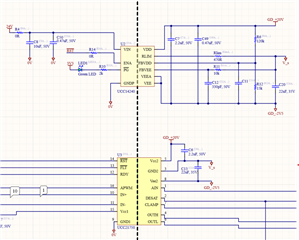

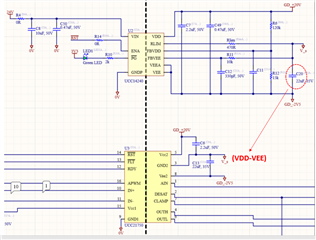

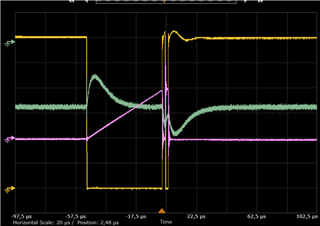

Hi, I am having some trouble with our UCC14240-Q1 implementation, we are using the UCC14240-Q1 in combination with the UCC21750 gate driver for a VSI design. In the picture below DPT data can be seen.

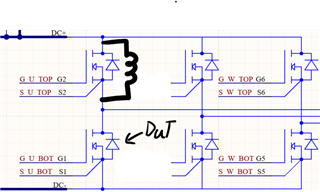

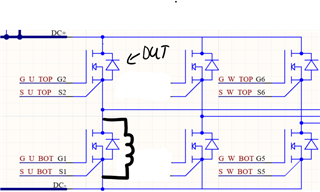

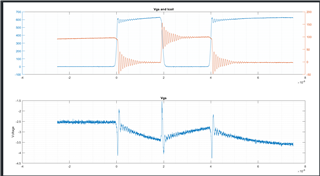

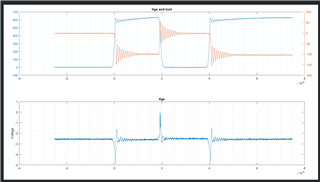

The pictures on the left shows bot as the DUT, while the Vgs measurement is of the top MOSFET. The picture to the right is when the top MOSFET is the DUT and the Vgs measurement is of the bot MOSFET.

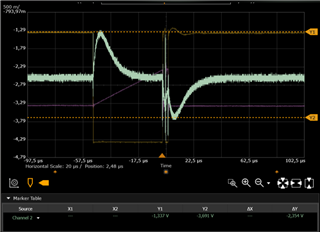

The issue seems to arise whenever the DUT switches, and has a very slow response time. As a similar drop of Vgs also happens at the start of the first long pulse when the DUT turns on the first time. picture of this can be seen below. (first spike is up to -1V3 from -2V5 and second spike is down to around -3V6)

Any input into what could be causing this would be greatly appreciated.