Hello experts,

I am having a problem with the MOSFETs getting damaged when we do SCD. We have designed two boards as potential fixes for this problem. Board A has 4 N Channel FETs in parallel on each CHG and DSG side (MPN: BSC061N08NS5) and Board 2 with a single N channel FET each on CHG and DSG side. (MPN: PSMN1R9-80SSEJ). The pack is 14S14P configuration with Panasonic 18650BD as cells.

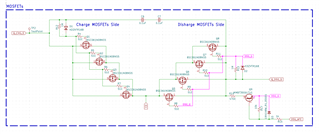

Board A Schematic:

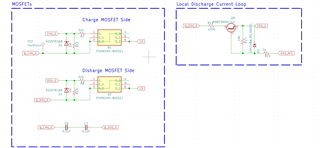

Board B Schematic:

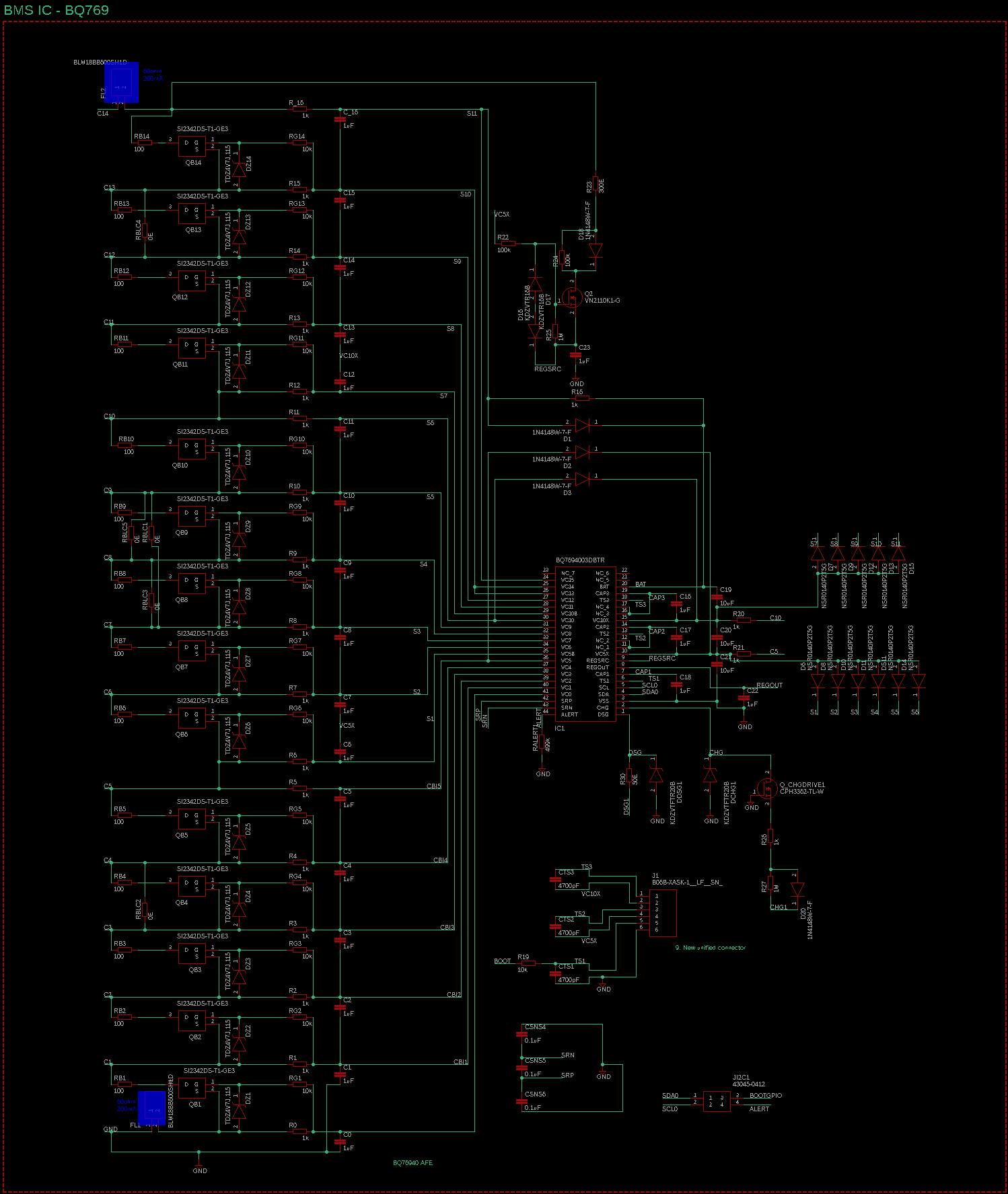

AFE Schematic from the BMS logic board:

We know that the AFE is detecting the SCD as we see the SCD alert flag being raised and our MCU controller being able to see and log the event. Based on suggestions from BQ769x2 app note, we have also added a local PNP turn off circuit to help dissipate the parasitic gate capacitance that the MOSFETs might have. With all these changes we are still failing SCD. The DSG MOSFETs are blowing apart and shows a short between source and drain.

As we had smaller test packs made we also tested with that. Here are the results.

- Board A - 14S1P - Cleared.

- Board A - 14S10P - Failed.

- Board A - 14S14P - Failed.

- Board B - 14S1P - Cleared.

- Board B - 14S10P - Cleared.

- Board B - 14S14P - Failed.

This makes me think the avalanche current rating of the MOSFET is the parameter that is making the difference because with the cells in parallel reducing the max current the pack can reach in a short also reduces. I also want to discuss the idea of adding a gate driver IC or even use a Battery Gauge from TIs portfolio as these devices are more equipped to handle large MOSFETs.

I will edit the post and keep adding more relevant information as the I do further tests. Please project your thoughts.

Best,

Abhijith.