Dear forum,

according to the device documentation "Device sets WD_PWRHOLD if hardware condition on pin DISABLE_WDOG (mapped to GPIO8 pin) is applied at start-up".

Unfortunately this is not working on our system.

After power-up we check via I2C from the u-boot bootloader:

-

Read register "GPIO8_CONF" offset 0x38 to ensure GPIO8 is configured as DISABLE_WDOG input pin

=> i2c dev 1 ---> 3 = Pin configured as DISABLE_WDOGSetting bus to 1 |||=> i2c md 48 38.1 01 7654 32100038: 6a j -> 0110 1010

-

Read status of GPIO8 via register "GPIO_IN" offset 0x3F reflecting high state of DISABLE_WDOG

=> i2c dev 1 -> GPIO8Setting bus to 1 |=> i2c md 48 3F.1 01 7654 3210003f: dc . -> 1101 1100 -

Read WD_PWRHOLD via register "WD_MODE_REG" offset 0x406 which is unexpectedly 0 (should be 1 as DISABLE_WDOG is high)

=> i2c dev 0 -> WD_PWRHOLD (Why not 1??)Setting bus to 0 |=> i2c md 12 406.1 01 7654 32100406: 02 . -> 0000 0010

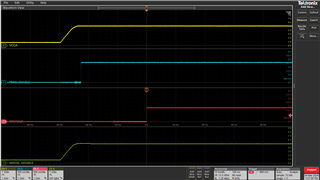

Please find below the oscilloscope capture of WDOG_DISABLE and nRSTOUT (MCU_PORz) during power on. There is roughly 20 mS of time duration of WDOG_DISABLE set high before nRSTOUT goes high. This fulfills the 30 uS requirement of tWD_DIS (DISABLE_WDOG input signal deglitch time).

For a more complete PMIC register view please find below the registers (just after power up) from I2C address 0x12:

=> i2c md 12 0.1 0b

0000: 00 00 3c 7f 7f ff 02 0a 00 bf 00 ..<........

...and the registers from I2C address 0x48:

=> pmic dev pmic@48

dev: 1 @ pmic@48

=> pmic dump

Dump pmic: pmic@48 registers

0x00: 00 9a 11 05 33 2b 22 2b 32 28 31 2b 31 1b 2d 2d

0x10: 2d 2d fd fd 73 73 b2 b2 1b 1b 1b 24 24 22 02 33

0x20: 33 00 00 f4 38 12 38 24 24 24 24 20 7f 00 00 00

0x30: 00 20 40 ba 01 1a 18 2a 6a 1a 1a 1a 19 08 00 dc

0x40: 08 55 75 01 2d 01 55 50 00 00 00 00 00 00 00 ff

0x50: ff 3f 11 02 30 00 00 01 08 07 10 00 00 00 00 00

0x60: 00 00 00 00 00 00 01 00 00 00 00 00 00 00 00 00

0x70: 00 00 00 02 00 00 00 00 55 01 55 99 00 43 00 00

0x80: 00 09 02 00 0f 00 00 00 00 00 00 0b ff ff 00 00

0x90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

0xa0: 00 00 00 80 00 00 08 00 00 00 00 00 00 00 00 00

0xb0: 00 00 00 00 00 00 00 00 01 01 00 00 00 00 00 00

0xc0: 00 00 00 e0 80 00 00 00 00 00 00 00 00 00 00 00

What reason could cause WD_PWRHOLD not to be set as expected?

Thank you and best regards,

G. Friedrich