Other Parts Discussed in Thread: UCC28951

I have odd behavior of a UC3875DWF. When a Power FET blows, it occurs after a number of weird "frequency drift with double-pulse" occurrences. The same IC on the same board will work most of the time. This 10V, 10A modulated AC supply drives the filament of a power tube. When the filament is cold it is almost a dead short. The supply runs until it hits a hardware current limit that pulls the CS+ pin to VREF, initiating another soft-start. This continues until the filament warms up. The worst case occurs at high line, when the duty cycle (phase shift) doesn't need to change much to generate an over-current condition.

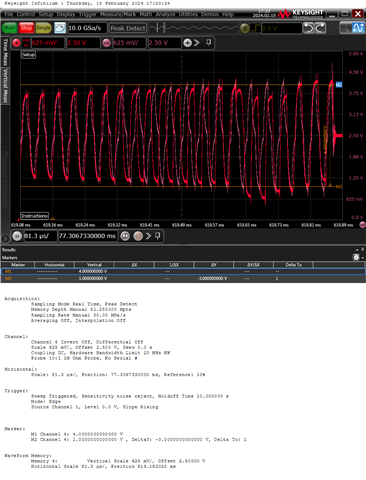

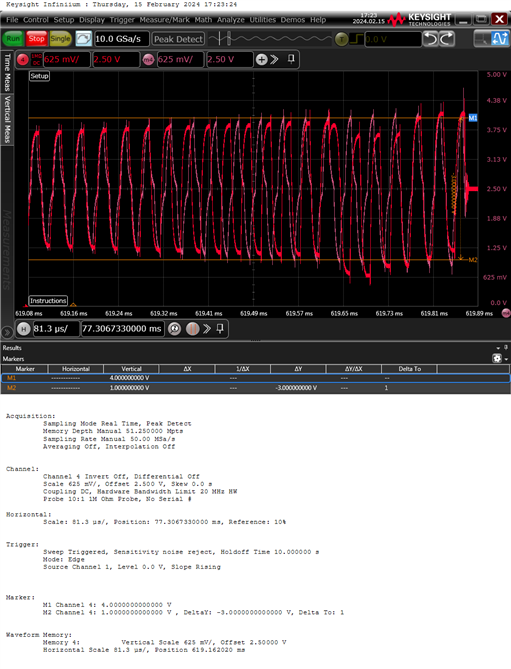

I've attached a screen capture of the schematic and transformer secondary current (because it's easy to measure without affecting the card) of two different start-ups. The purple trace in "m4" is a normal startup that had no issues. The red trace in "4" failed a Power FET. The red trace matches the purple one with an identical constant operating frequency... until it doesn't, as shown here. The first five cycles have the correct operating frequency. The frequency then seems to increase linearly until it is 180° out of phase from what is expected after five more cycles. After five more cycles we are nearly 360° from expected and then the oscillator seems to 'skip back' to normal and a double-pulse results. As a result, the capacitively coupled transformer primary is offset and while on its way to recovery an over-current occurs. About 50ms later the soft-start phases on and the situation repeats... until a FET blows.

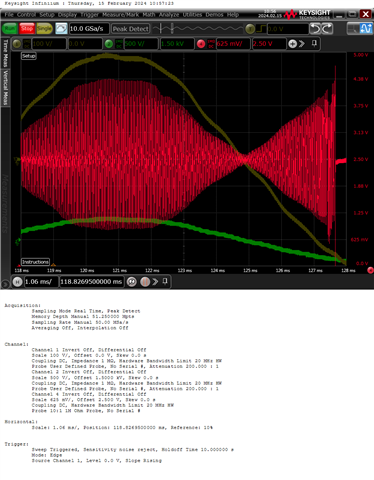

The third image shows how the phase shift controller is modulating the rectified 60Hz AC Mains... until the glitch near the end and the subsequent over current trip.

Looking at the datasheet, I see nothing that would affect the oscillator frequency. A schematic is attached and what you don't see is a discrete scaling and integrator stage that drives the IC error amp as a buffer.

What could be happening? What should I look at next?