Other Parts Discussed in Thread: TPS922055

Hi Team,

Use TPS922055 driver LED lamp, 36V power, output voltage 20-25V, current 3.5A.

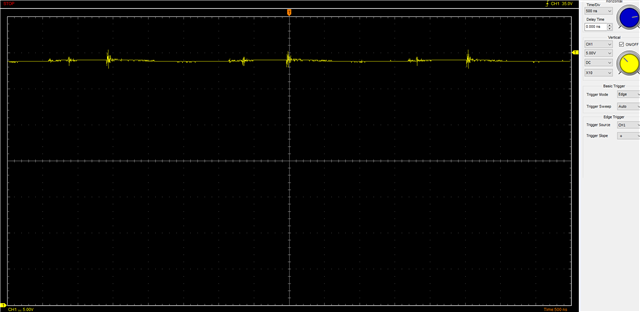

Use the oscilloscope to check the chip 14 pin SW, when the PWM is less than 10%, the output waveform interference is large (PWM is more than 20% waveform is better).

Double-sided circuit board design.

There are two sets of independent output circuits on a circuit board.

36V power waveform also has large interference, how to improve?

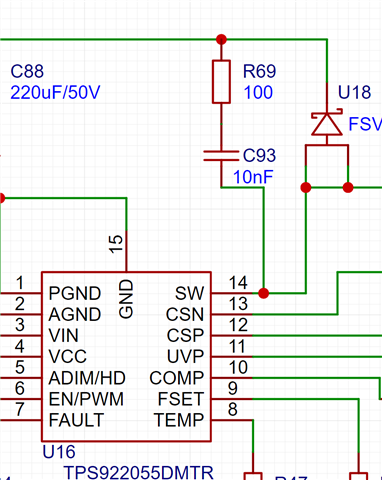

The schematic diagram is as follows:

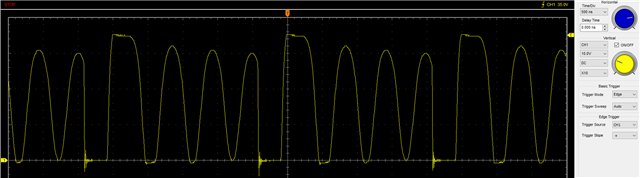

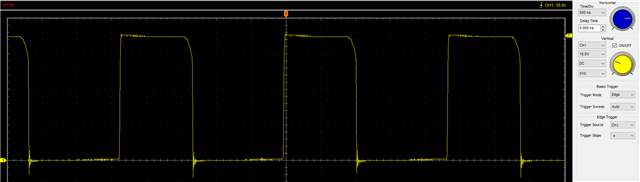

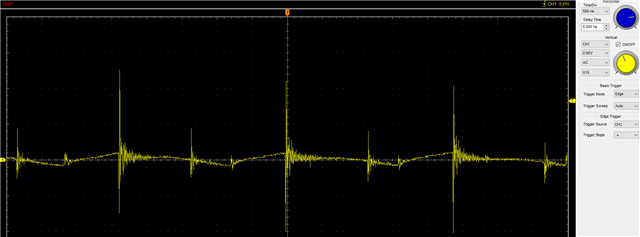

SW waveform diagram is as follows: (@10%PWM)

SW waveform diagram is as follows: (@20%PWM)

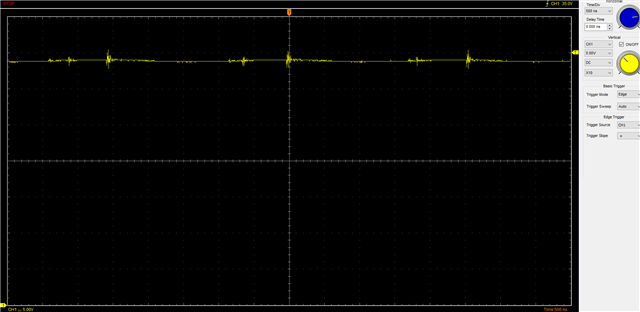

36V power waveform diagram is as follows:

Best Regards,

Kevin