Other Parts Discussed in Thread: SN6501,

Hello TI team,

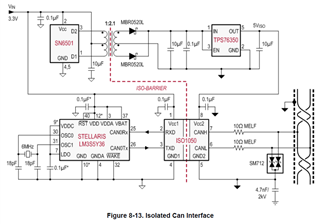

I need to implement an isolated CAN Bus node based on the spec sheet recommended design of the transformer driver SN6501.

Question 1

I would like to use the LP2981A-50DBVR 5V LDO regulator for this application instead of the TPS76350-Q1 which has a current limit that is too high for my needs (800mA typ). Indeed, the LP2981A-50DBVR 5V LDO regulator has a low current limit which is appropriate for my application (150mA typ). The spec sheet for the LP2981A-50DBVR LDO regulator recommends to add an effective output capacitor (4.7uF) with some ESR for loop stability. I would like to use ceramic capacitor instead of tantalum. The spec allows the use of ceramic capacitor if a 1ohm resistor is added in series with the capacitor. So, giving that the CAN transceivers (TCAN1051HGDR ) and signal Isolator (ISO6721BDR) will both have ceramic decoupling capacitors on their power pins, will these decoupling capacitors cancelled the ESR of the provided capacitor+resistor arrangement at the output of the regulator? Will all the ESR of the ceramic decoupling capacitors parallel since all the components are very packed on the isolated side?

Question 2

In order to get 4.7uF of effective capacitance, 2 capacitors need to be installed in parallel to get this value because of ceramic capacitor DC bias. If more than one capacitor is used at the output of the regulator, is the series resistor need to be spitted? 2ohm added to one capacitor and 2ohm added to the other capacitor? Can the total resistance be added to one capacitor only?

Question 3

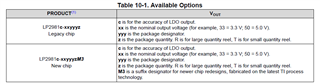

The LP2981A spec keeps referring to this “new chip” which has better dropout voltage and is stable with low ESR ceramic capacitors. The IC has a “M3” suffix. Is this IC available?

Thank you,

Regards

Eric