Hi

We are using the BQ40Z50 in an application where we have 3 possible scenarios for battery discharge

1: The battery can be discharged very slowly if left in storage for very long periods of time (weeks) DSG FET off NR = 0

2: The battery pack can be discharged slowly if left idle for long periods of time.(Hours) DSG FET on.

3: The battery pack can discharge quickly when in in active use under high loads (minutes) DSG FET on.

Ideally we don't want the cells to discharge below 3 volts when in any mode.

A 3V CUV threshold causes issues when the device is in active mode under high load because the voltage can drop well below that threshold for periods of time but the voltage will bounce back when the load is stopped..

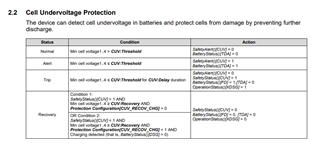

Reading the TRM it seems the CUV or CUVC are the only way to terminate discharge while staying in active mode is this correct?

I would like some advice on how to set the thresholds so they will work for scenario 2 and 3.

I would also like some advice on the best approach to minimize further discharge in scenario 1 when the DSG FET is already off.

Regards

Ian