Other Parts Discussed in Thread: INA280

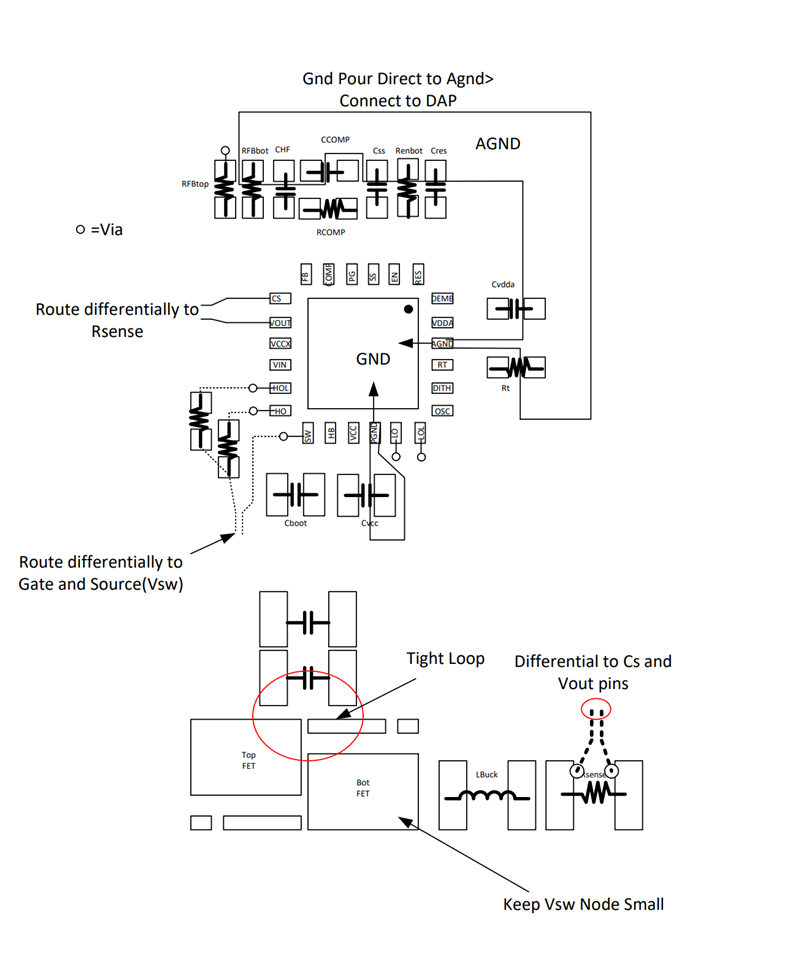

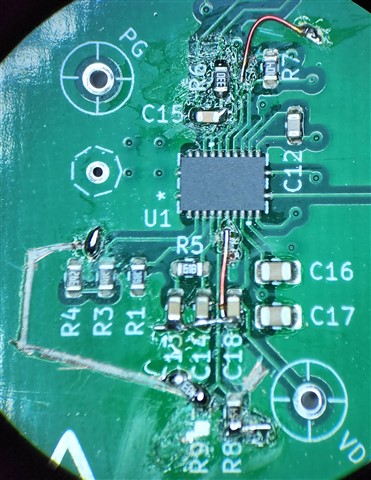

I am developing a power converter based on the LM25148. My first design was not stable and I could not diagnose the problem so I backed up to the typical design #2 in the datasheet. I recreated the design using nearly identical parts and closely copied the layout from the LM25149EVM. See the schematic below:

The only change I made from the reference design was increasing the output voltage from 5V to 12.8V. I increased the voltage rating of the output capacitors accordingly. The INA280 was supposed to measure the inductor current for troubleshooting but may have been a poor choice due to bandwidth and saturation limits.

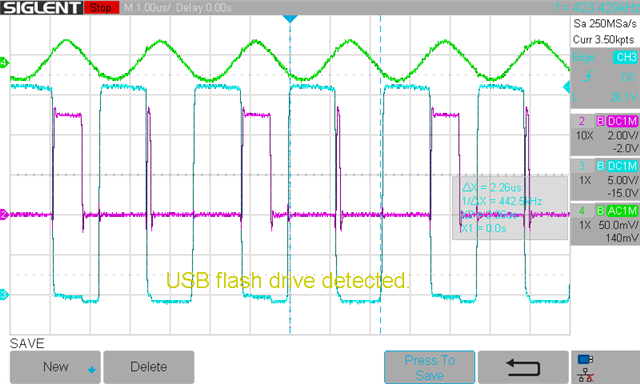

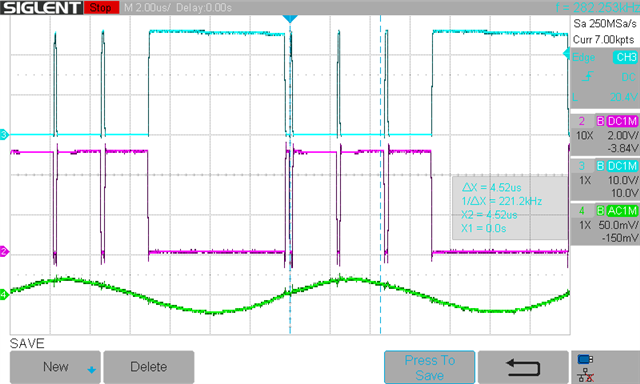

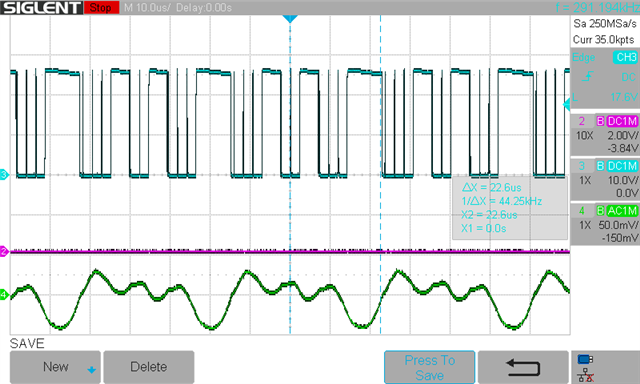

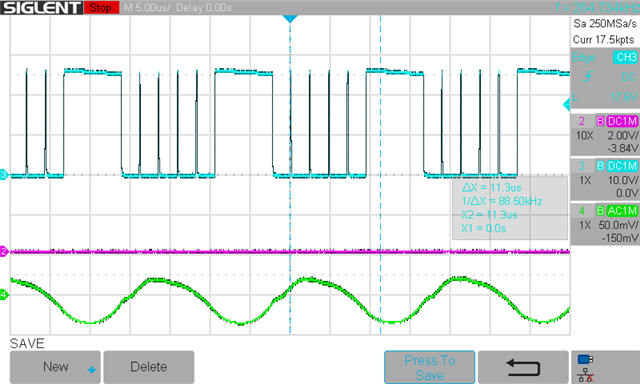

At loads above ~3.5A I begin to see inconsistent switching as demonstrated in the scope shot below. The blue trace is the SW node and the green trace is Vout.

Longer pulses are followed by shorter pulses (the smaller pulse width looks like minimum on time).

This behavior is load dependent and exhibits some hysteresis when the load increases and decreases. More specifically the instability will begin at a certain increasing load, and remain even when the load drops below the draw when the problem began.

I have used the TI design calculator to check my design, I should have a more than adequate 78 degree phase margin and a -18dB gain margin. I have taken the following steps to fix my problem:

1. Add a filter to the ISNS+ and Vout pins as used in the EVM

2. Adjust my compensation network to account for inaccuracies in my overall transfer function analysis

3. Purchase and test the TI produced EVM to rule out test equipment problems

The EVM from TI seems to work fine and rule out my test equipment as a problem, though there are always possible edge cases. I have taken other steps to troubleshoot the device such as various filter and configuration adjustments, but these changes did not help and I did not document them well.

I feel like I am slightly losing my mind as I cannot see why the EVM works but my design does not. I can supply layout files and any other scope shots if that will help.