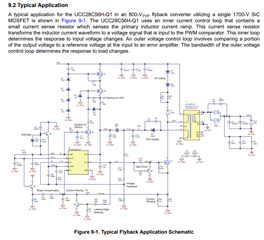

Other Parts Discussed in Thread: UCC28C50,

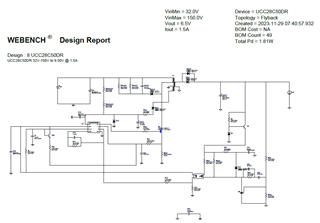

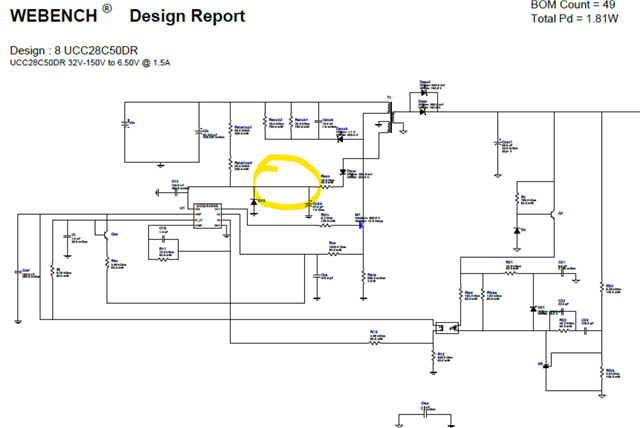

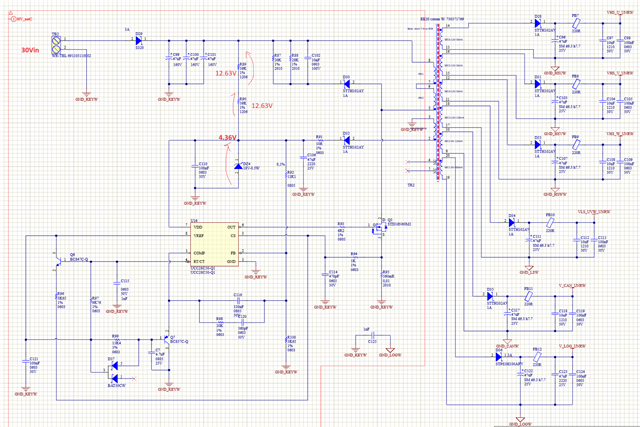

Starting from these Flyback PSR and SSR Webench designs:

webench.ti.com/.../SDP.cgi

webench.ti.com/.../SDP.cgi

I've just buld up 2 build up 2 circuits using a custom multiout transformer.

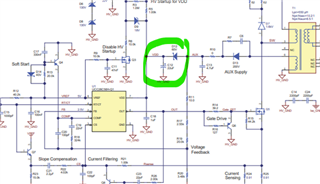

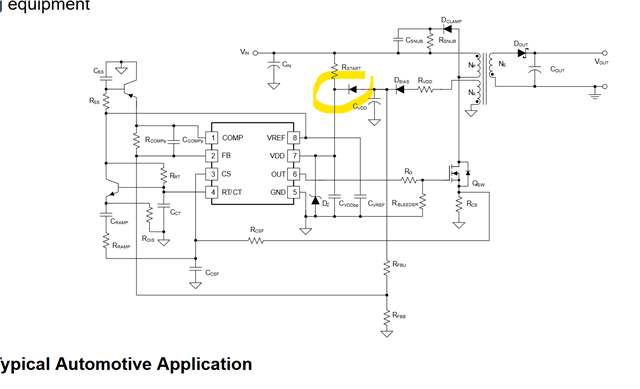

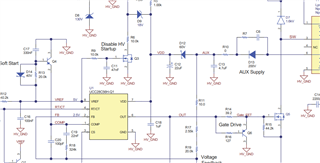

While the SSR circuit seems to startup and regulate properly, the PSR does not start. The cirscuis is the following and replicates the Webench design:

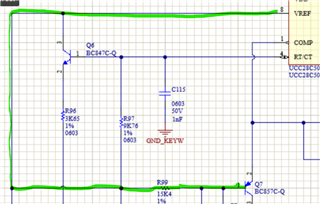

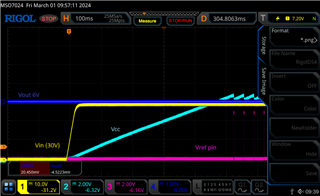

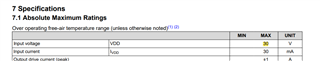

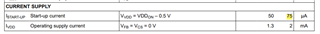

Doing some measures @30Vin I noticed that voltage at Vdd pin7 UCC28C50 stays a lot below it's Vddon threshold (4.36V as pointed out on schematic).

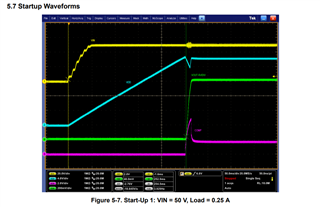

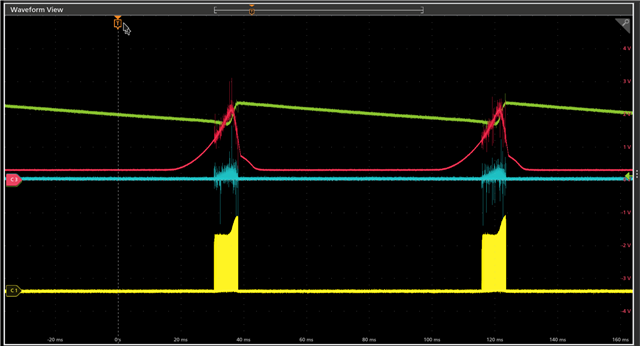

Stayin below 30Vin I could startup the IC just bypassing for a short time the 2 startup resistors R89-R90 seeing the oscillation start of the controller and the Vouts at no load. Applying a minimal load however, outs drops without anuy regualtion.

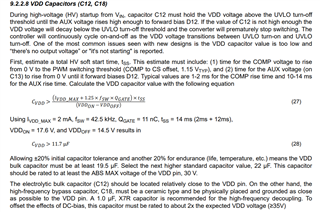

I have the doubt that the generated Webench PSR schematic is correct? In my opinion there's should be a decupling diode beetween the startup resistors and the rectified voltage coming from the primanry auxiliaty winding...