Other Parts Discussed in Thread: BQ25798

Hi

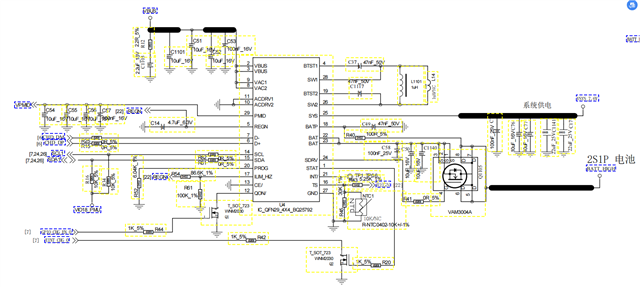

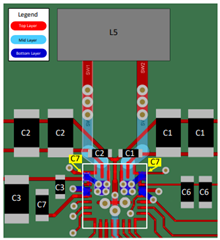

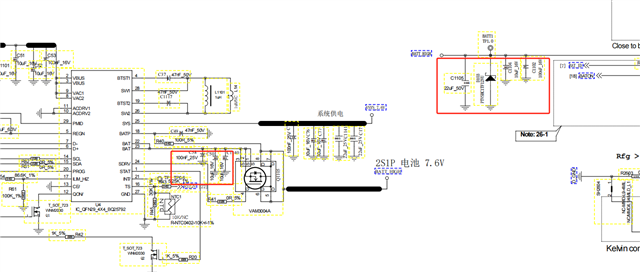

The customer design with BQ25792.

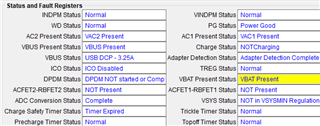

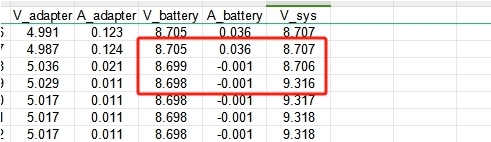

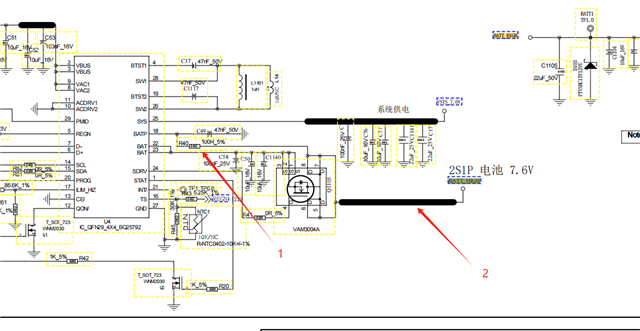

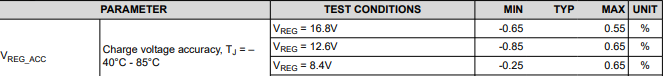

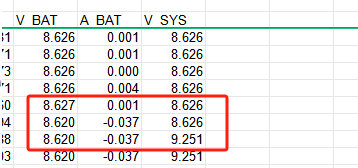

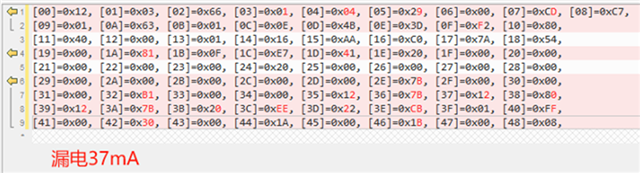

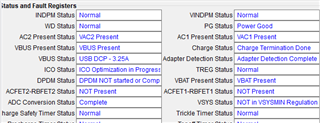

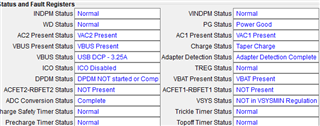

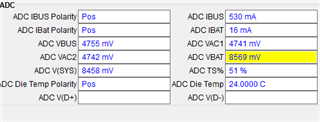

The battery is not turned off after it is fully charged and charging is stopped. There is still a current output of 38mA. There are also cases where the battery has a leakage current of 1mA after charging is stopped. Can any problems be detected by measuring the signals of the following two phenomena? When charging is stopped, the SYS voltage will jump from equal to the battery voltage to 0.6V higher than the battery voltage. Is this normal?

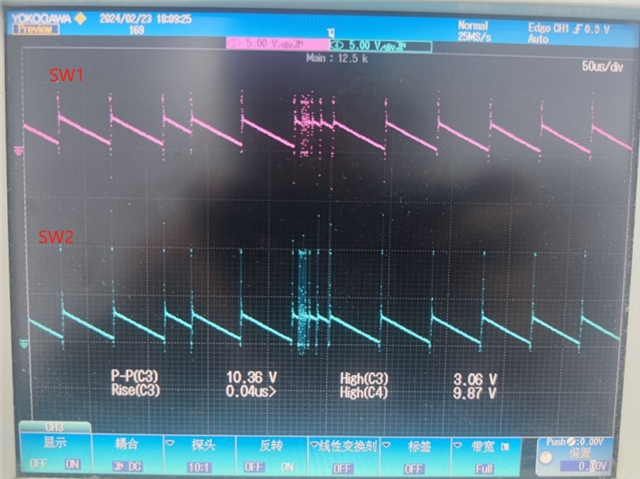

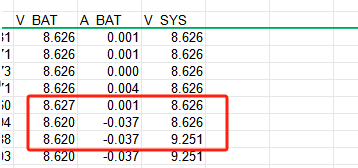

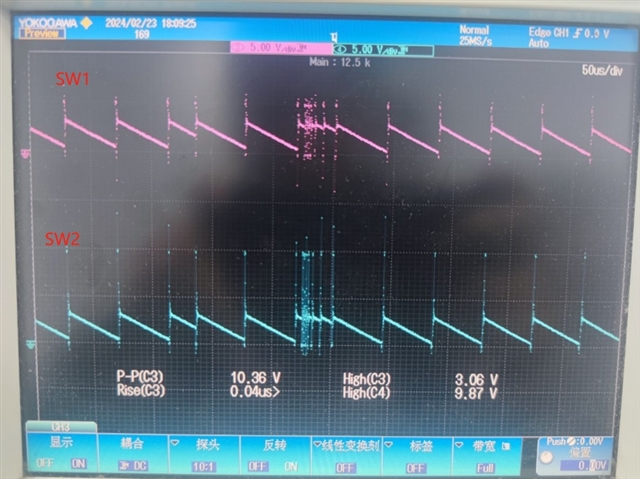

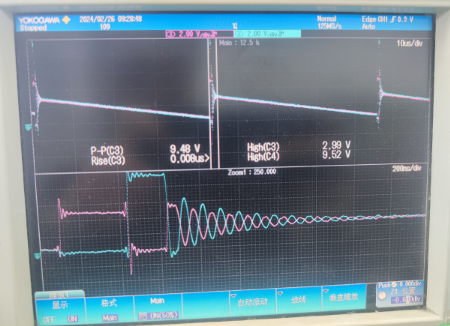

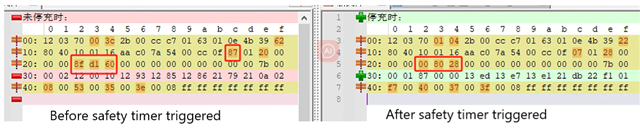

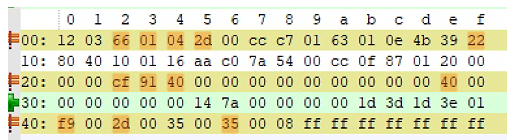

The measured waveforms of sw1, sw2, V_bat, and V_SYS under the two phenomena are as follows:

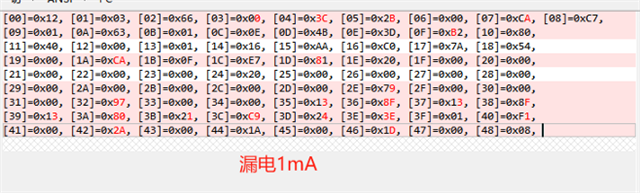

1. Leakage current 1mA waveform after charging:

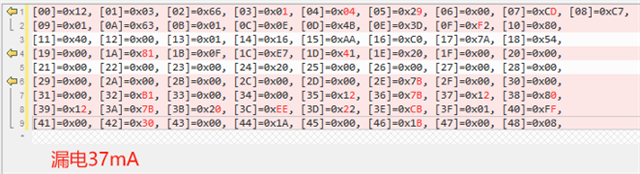

2. The leakage current is 38mA after charging is terminated. When measured, the battery voltage and SYS voltage are similar to the picture above, which are also 0.6V higher.

The abnormal waveforms of sw1 and sw2 are as follows:

Please help check it.

Thanks

Star

.

.

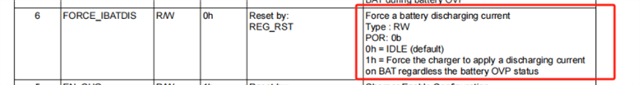

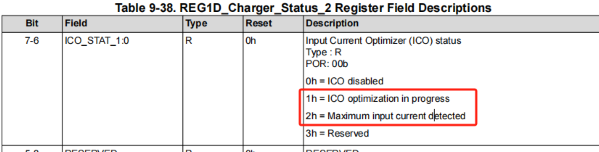

. Why is that turned on?

. Why is that turned on?

is on. Why? I do not recommend this.

is on. Why? I do not recommend this.