Respected TI experts:

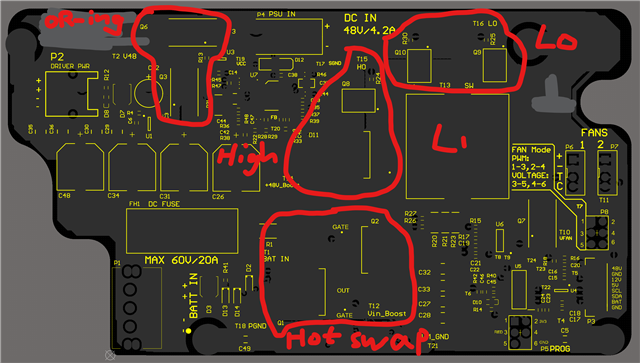

I have designed a new PCB which includes hot swap circuit, boost converter (with controller LM5122) and OR-ing circuit. Could you please review my design and provide me some suggestion?

Here are some information of the PCB:

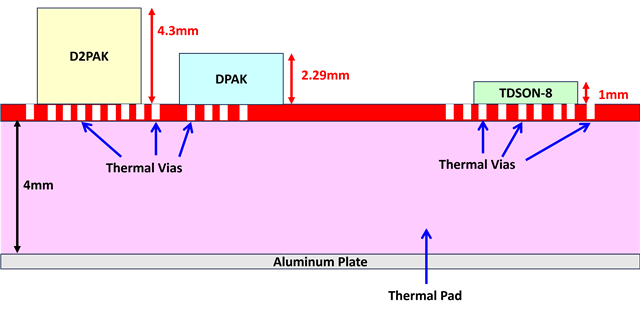

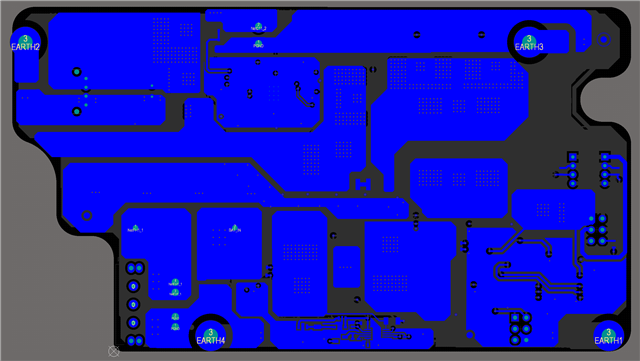

- 4 layer board

- 2 OZ

Please allow me to explain some key points of this new PCB layout:

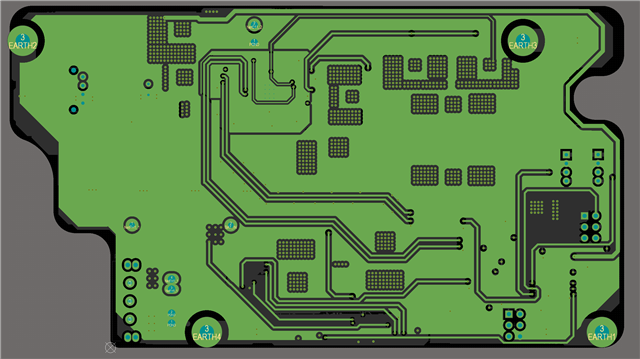

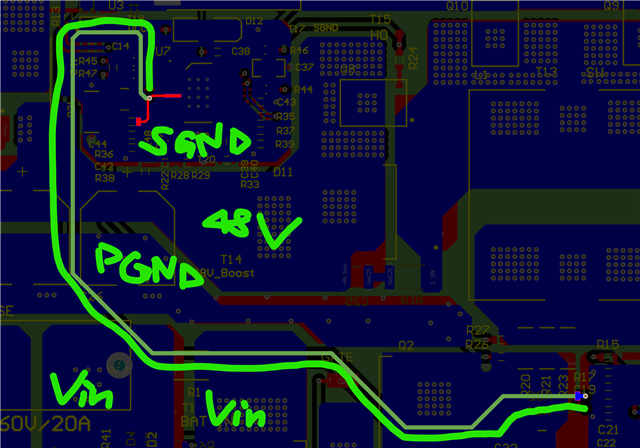

- Power flow/high current runs on both the top and bottom layers.

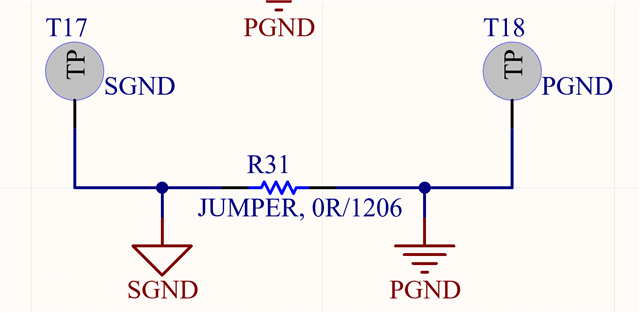

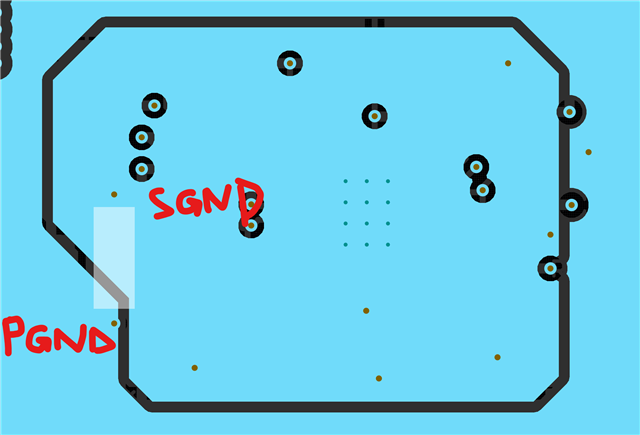

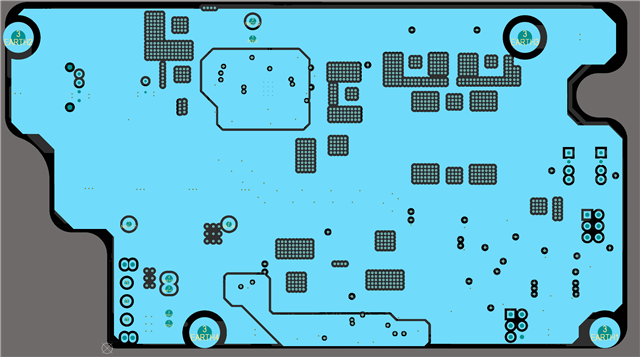

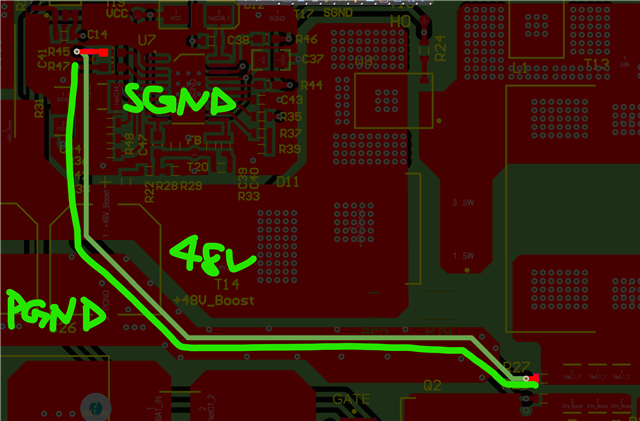

- Some signal traces run on the inner signal layer, while the remaining pieces on the inner signal layer are SGND (signal ground of boost) and PGND (power ground).

- The inner GND layer includes three different grounds: PGND, SGND, and LM_GND (hot swap GND). PGND is large and clear.

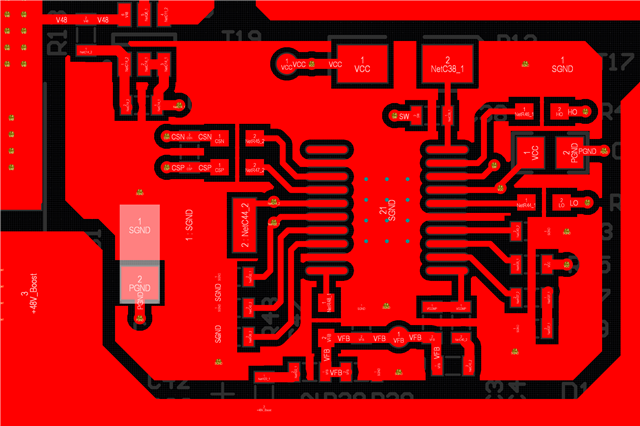

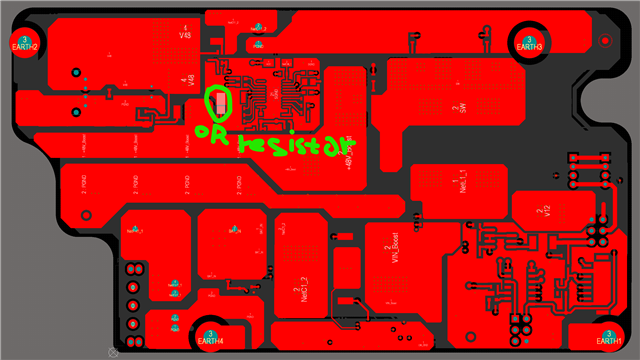

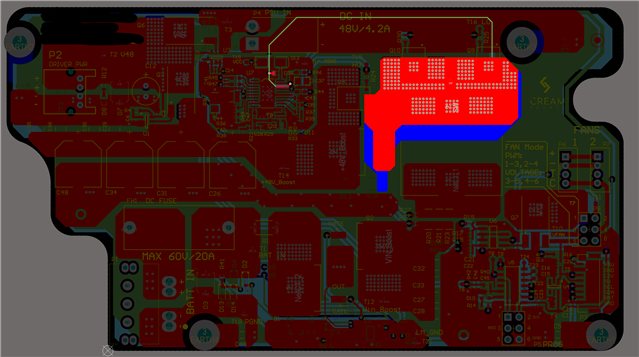

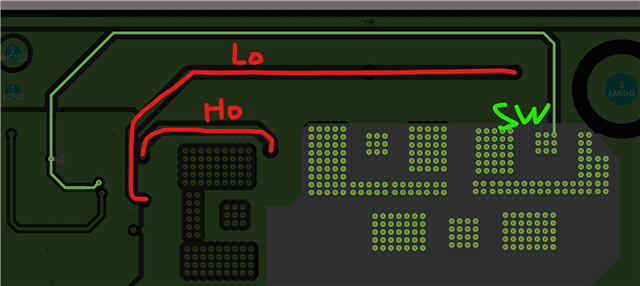

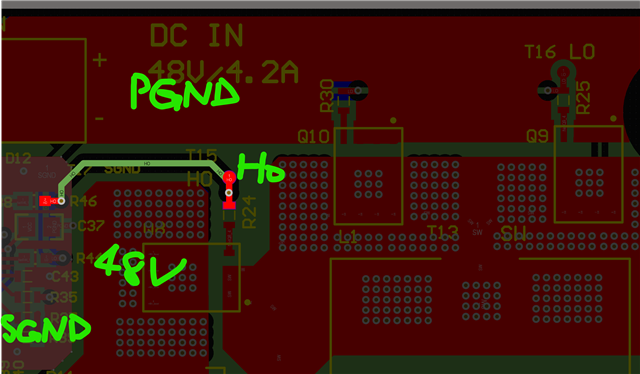

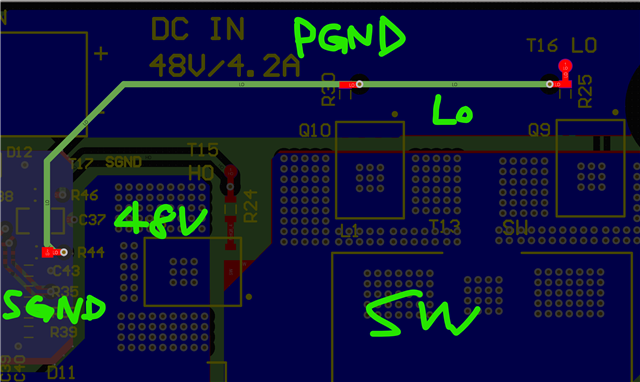

- The noise source is the SW node, which is the drain of the low-side MOSFET. It is also the hottest area. I have balanced the size of this area to dissipate heat adequately without emitting noise. Please see the highlighted area in the picture below:

The boost controller needs to sense this voltage as a reference for the high-side MOSFET. Therefore, there is a trace from this area to the IC. However, this trace does not overlap with the control signal (highlighted in RED) and is placed as far away from the control signal as possible. It also runs on the PGND copper.

- Low-side and high-side MOSFET control signals run on the PGND copper (top, bottom, and inner GND layers) and are placed away from the stable 48V and SW.

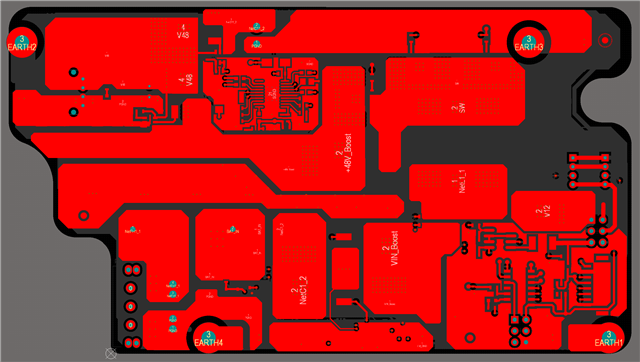

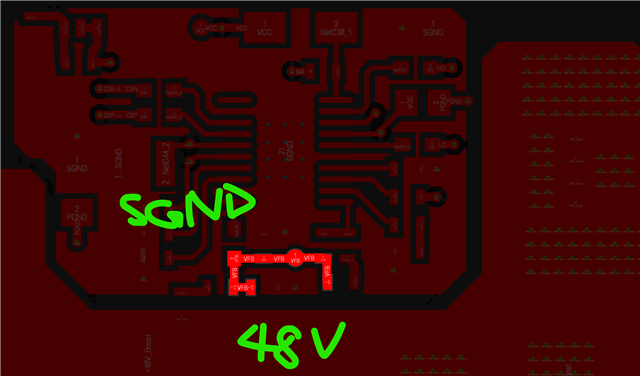

- The output voltage feedback signal is very short and runs on the SGND copper.

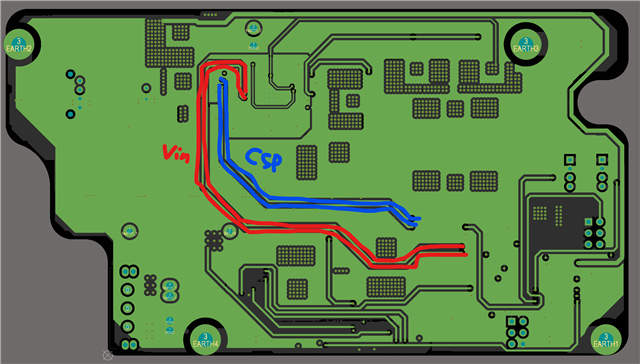

- Input current sensing signals (CSP, CSN) run on the PGND copper and stable 48V copper.

.

.

- Input voltage sensing signals run on the stable DC input voltage coppers, PGND copper, and stable 48V copper.

- The input voltage sensing signal (highlighted in RED) and current sensing signal (highlighted in BLUE) are placed as far away from each other as possible, and their routes avoid the noise area.

- All MOSFETs and inductor have many vias (NOT tented) on the pads. Moreover, there are many vias (tented) used to conduct heat to the bottom next to the MOSFETs and inductor.

- A 48V trace flows from output at left-top corner to the header at the right hand side.

Any suggestions are opinions are appreciated. Thank you very much.