Hi Team,

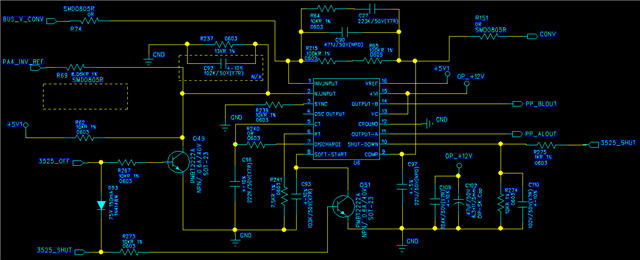

Please refer to the schematic,

Customers use UC3525 to create push-pull topology;

CH1: Vo (yellow)

CH2: COMP (pin 9/green)

CH3: OP+ terminal (pin 2/blue)

CH4: OP - terminal (pin 1/red)

Under normal circumstances, pin4 will follow the pin3 waveform (pin4 is higher than pin3, comp low level, duty off; pin4 is lower than pin3, comp high level, duty).

However, in the middle of the reference waveform, pin4 is lower than pin3, and comp still maintains the low level for about 1 ms before turning to the high level.

Under normal circumstances, COMP will immediately reflect the difference between the two ends of the OP.

However, when a specific load is instantaneously switched (such as waveform), COMP will reflect the delay.

What could cause this phenomenon?