Other Parts Discussed in Thread: TPS6521905

Hi, TI expert

A customer has a question while reviewing TPS65220.

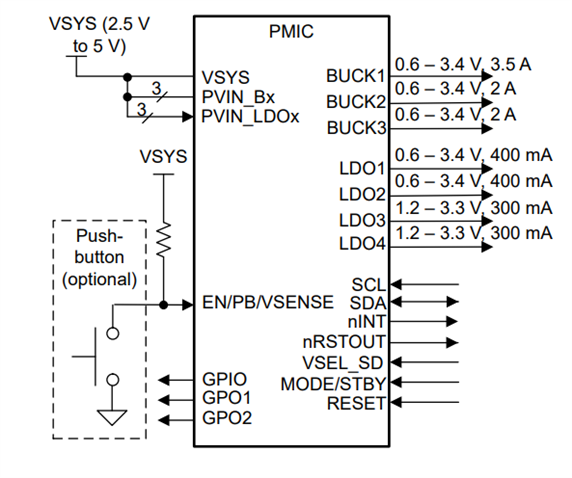

Q1) The attached file is a TPS65220(PMIC) block circuit diagram, and we would like to request a circuit review before PCB Artwork.

Q2) The information below is what the F/W manager inquired about. Please review the contents.

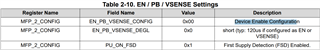

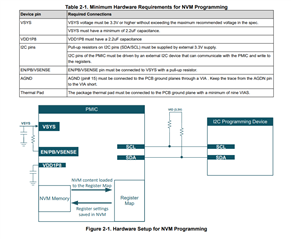

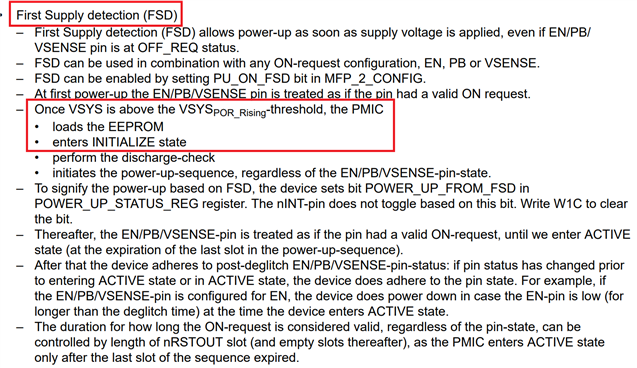

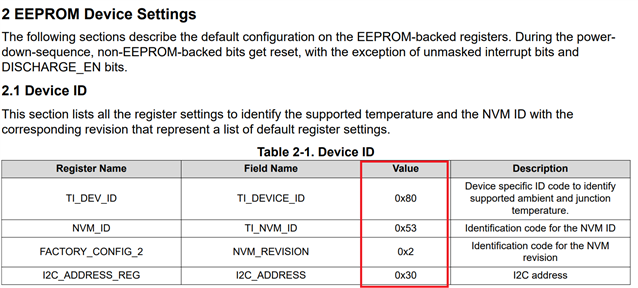

- I'm curious if the default values in the TPS6522053 Technical Reference Manual are correct for the PMIC. Initially, when power is supplied to the PMIC as shown below, it always enters FSD (First Supply Detection) Initialize mode and retrieves EEPROM values. Could you confirm if the default values mentioned in the manual are accurate?

Please check. Thank you.