Other Parts Discussed in Thread: UC1843B-SP

Hello,

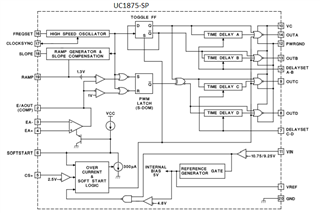

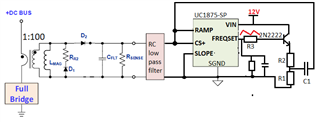

In my previous thread for the UC1875-SP (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1292405/uc1875-sp-configuring-slope-and-ramp-pins-for-cmc-with-slope-comp) it was explained that external circuitry is needed to support CMC slope compensation.

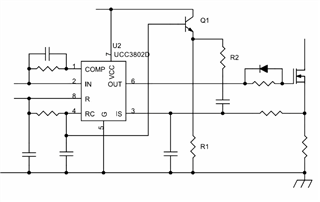

To do this, I've found two methods (UCC3802D article):

(1) The slope comp ramp can be added to the reference voltage (VREF pin)

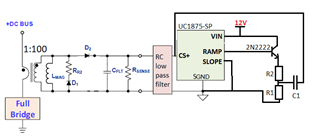

(2) The slope comp ramp can be added to the current sense signal (CS+ pin)

For (2), I've come up with the following scheme:

The sawtooth signal generated at the RAMP pin drives the NPN. By way of the resistor divider R1,R2 , a ramp voltage is also generated and that signal is AC coupled into the CS+ pin by means of capacitor C1. I wanted to verify this was the correct approach.