Other Parts Discussed in Thread: LM51551, LM5155

hi expert

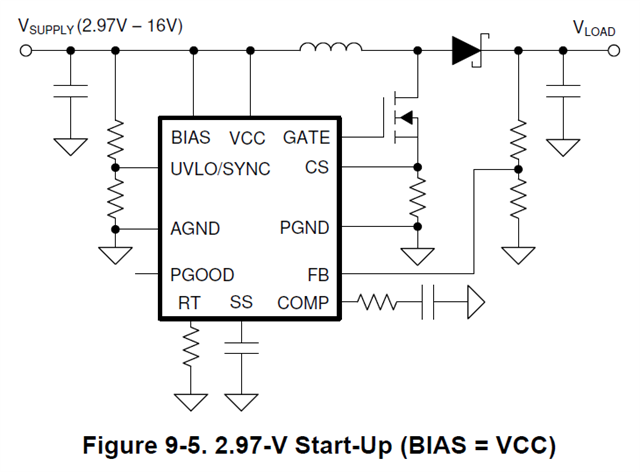

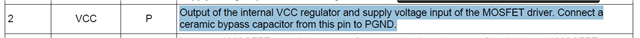

i saw the VCC pin function from datasheet--"Output of the internal VCC regulator and supply voltage input of the MOSFET driver. Connect a

ceramic bypass capacitor from this pin to PGND.".

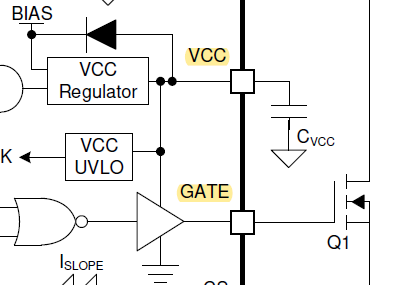

from the LM51551 block diagram, it seems like VCC only supply to pre-driver of GATE.

i have some questions about this architecture.

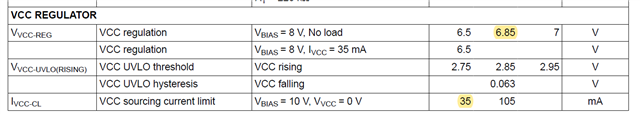

Q1: if bias is connected to a high voltage, then VCC regulator(LDO) will withstand large voltage. what about the efficiency of VCC regulator?