Hi team,

In datasheet, T_Reverse delay is defined Typ.0.45us/Max0.75us. Can customer estimate this time on their use case?

Regards,

Youhei MIYAOKA

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

In datasheet, T_Reverse delay is defined Typ.0.45us/Max0.75us. Can customer estimate this time on their use case?

Regards,

Youhei MIYAOKA

Hi Miyaoka,

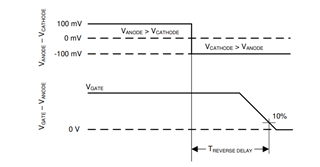

T_Reverse delay is shown as a graph in the datasheet. It is the time of (some propagation delay + FET to turn OFF) after it detects -100mV drop across the FET. Since the FET is discharging here, it depends on the gate capacitance. Only thing to note here is that the discharge current is very high(~2.37A), changing the gate capacitance will not change the time by much.

Hence, more or less the time should be same with change in systems.

Regards,

Shiven Dhir

Hi Shiven,

Thank you for your answer and additional description.

Regards,

Youhei MIYAOKA