Other Parts Discussed in Thread: AM6422, , TPS65220, USB2ANY, TPS62A02

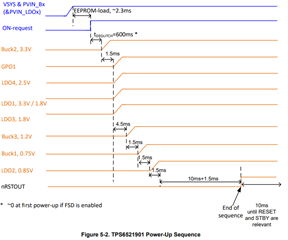

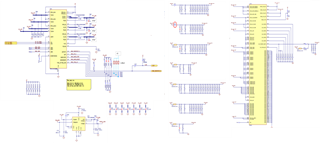

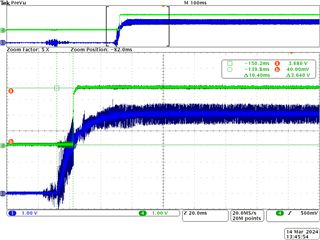

I have a question about the circuit that supplies power to the AM6422 using TPS6521901. The power is only outputted three times before it stops.

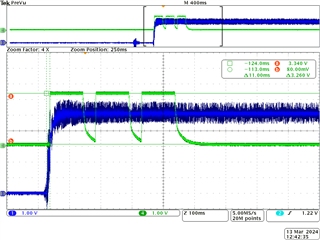

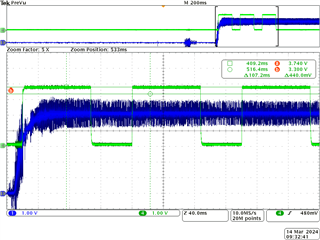

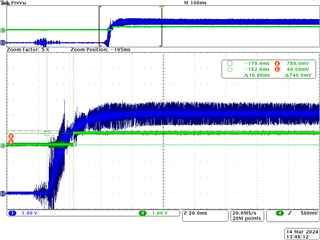

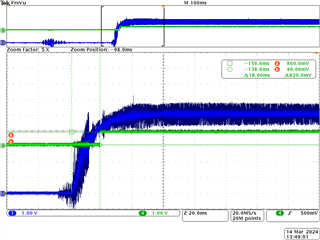

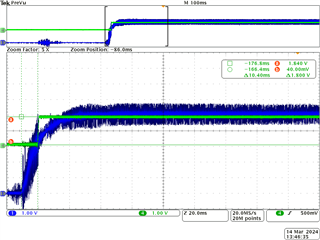

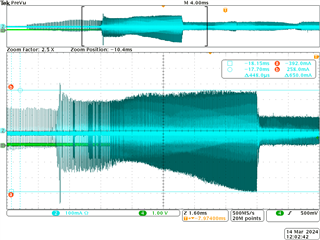

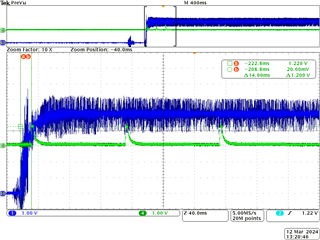

Blue: VSYS(5V)

Green: Buck2(3.3V)

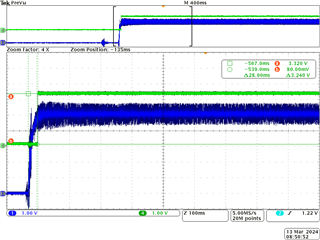

It appears that there is a fault and it is going through two retries before shutting down. In the output voltage waveform, the outputs of Buck3 (1.2V) and LDO2 (0.85V) seem to be abnormal.

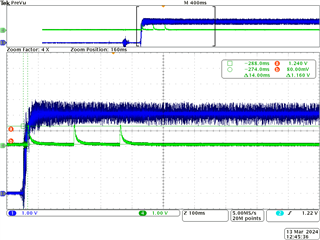

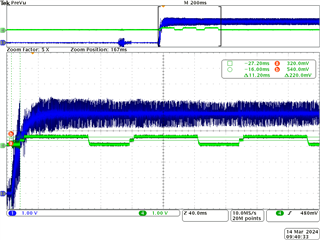

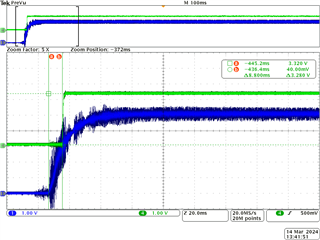

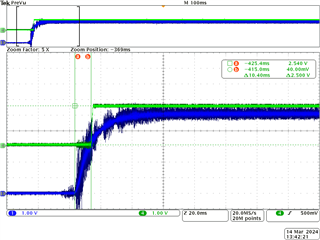

For the 1.2V output:

Blue: VSYS(5V)

Green: Buck3(1.2V)

The output voltage drops faster compared to the 3.3V output.

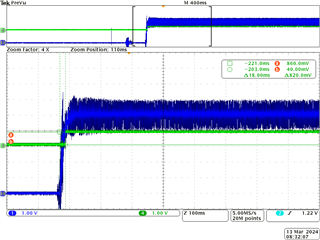

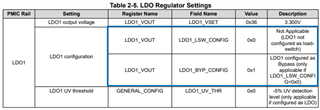

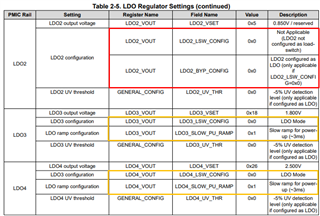

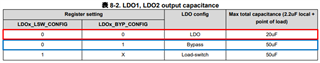

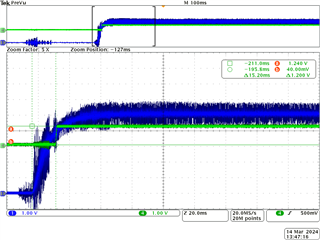

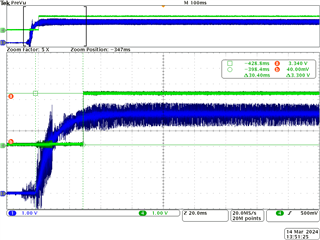

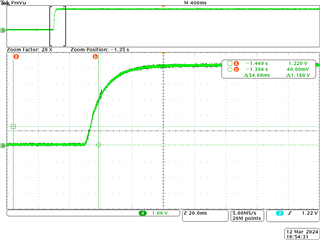

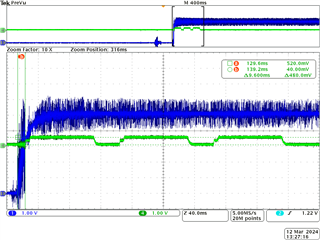

For the 0.85V output:

Blue: VSYS(5V)

Green: LDO2(0.85V)

The output voltage rises in a stair-step pattern.

The output voltage reaches around 0.5V.

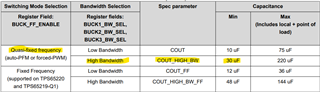

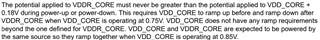

I have referred to the forum link provided and made the modifications to the capacitors for Buck1-3, but there has been no improvement. Please provide advice on how to resolve the issue.

Reference source