Hello,

For the Semi bridgeless PFC using UCC28070, can you please help answer this question:

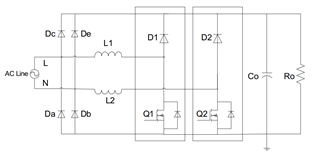

How does the controller identifies if the PFC configuration is interleaved or semi bridgeless. Our understanding is the controller generates output 180 degree out of phase between the 2 FETs which is needed for interleaved PFC but not for Semi bridgeless.

We are referring to this document below but could not find the differentiating factor between the two topologies for controller operation.

UCC28070 Implement Bridgeless Power Factor Correction (PFC) Pre-Regulator Design https://www.ti.com/lit/an/slua517/slua517.pdf

Thank you, Keith