Hi,

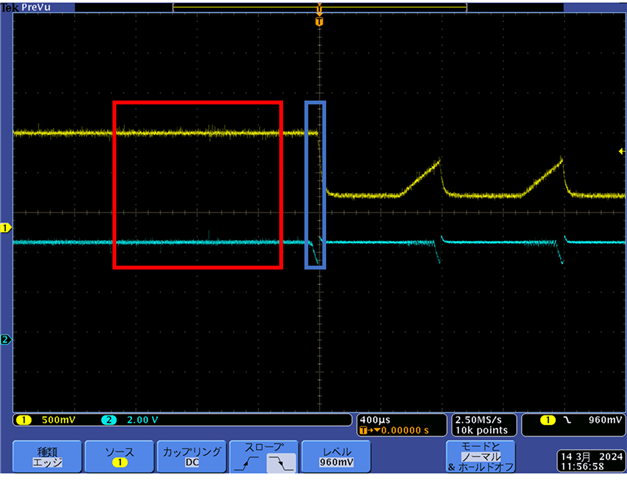

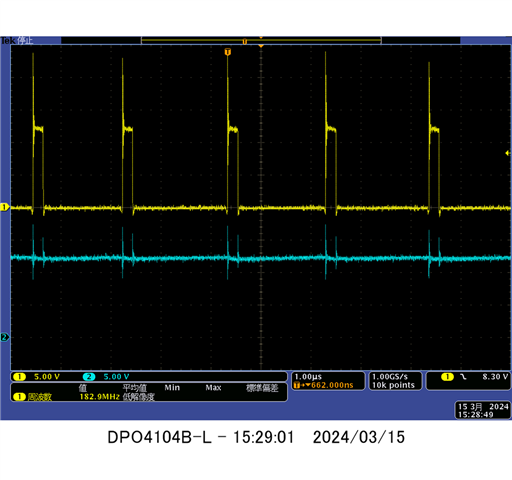

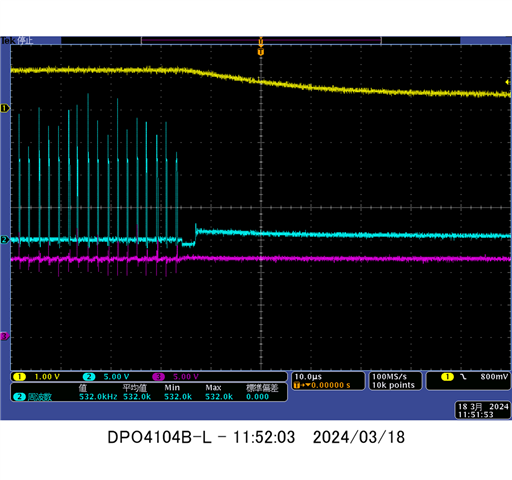

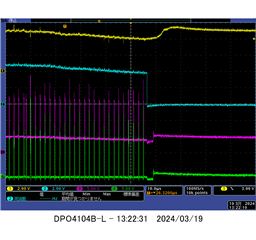

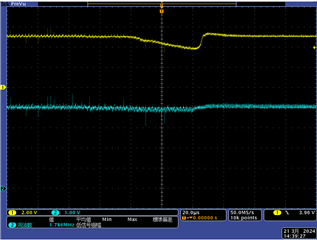

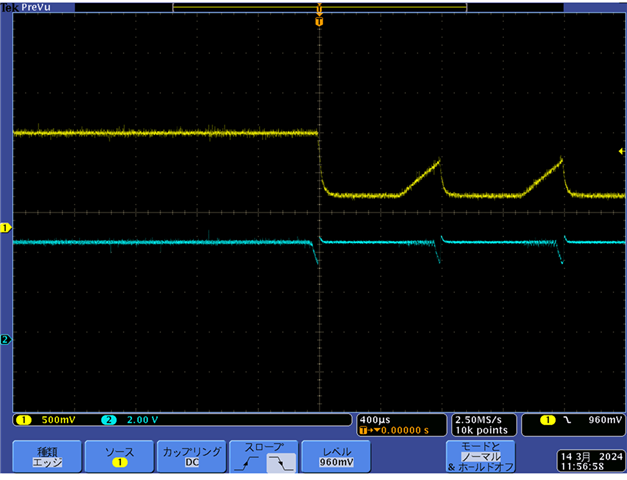

When the load device is Enable, the VREG drops and the VOUT (1.2V) stops. After about 6us, the VOUT/VREG rises and stops again.

This appears to be a VOUT (1.2V) stop because the VREG pin is below the threshold of 3.95V. However, the VDD pins (4.5V to 25V) and EN pins (0.6V) do not fall below the threshold for a moment.

Do you know the cause of this?

In the following waveform, Ch1 is VOUT and Ch2 is VREG.

A schematic is attached.

Best Regards,

Nishie