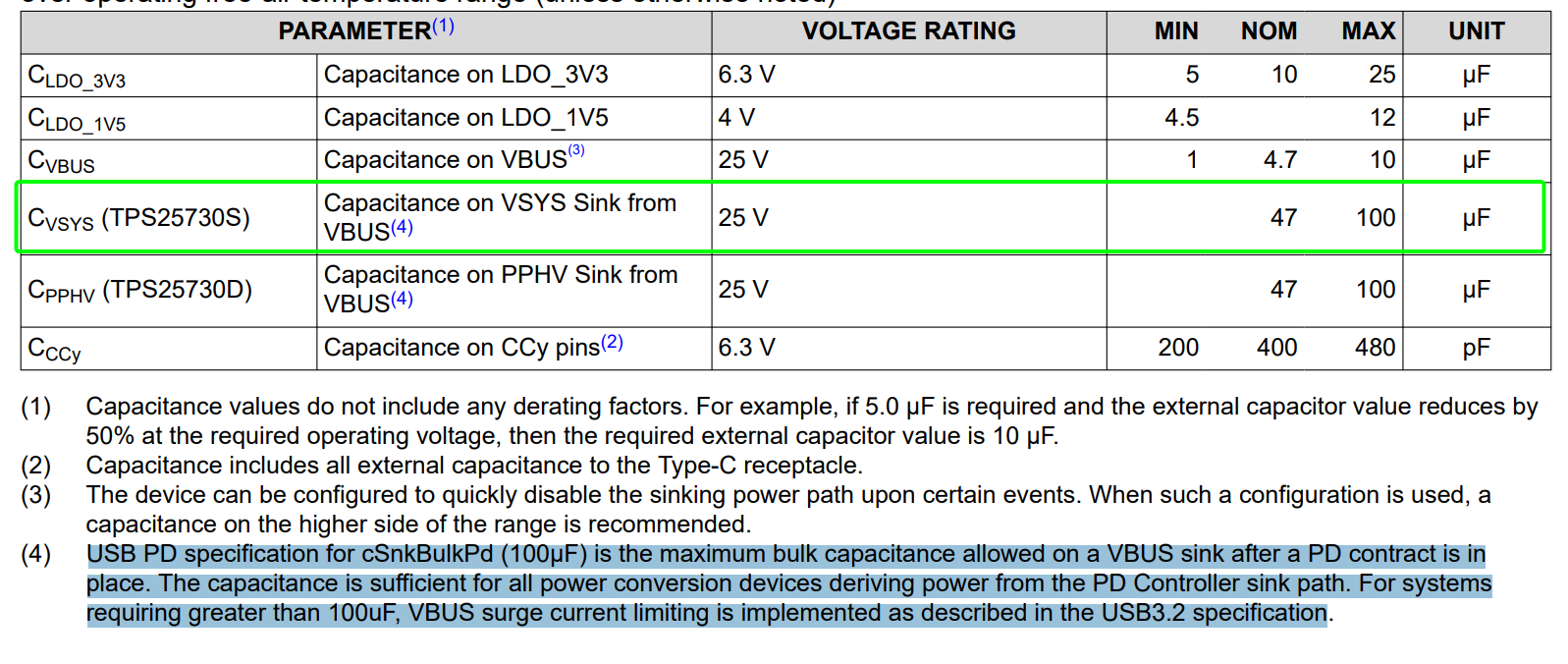

I am using the TPS25730S in my design. The datasheet says you can only have a maximum of 100uF of capacitance on the VSYS output. I have a larger load in my system that when switched on requires more than 100uF of capacitance to keep my voltage rail stable. You also have a note that says: "USB PD specification for cSnkBulkPd (100µF) is the maximum bulk capacitance allowed on a VBUS sink after a PD contract is in place. The capacitance is sufficient for all power conversion devices deriving power from the PD Controller sink path. For systems requiring greater than 100uF, VBUS surge current limiting is implemented as described in the USB3.2 specification". Is there a recommended solution on how to handle having more than 100uF of capacitance on the VSYS output of the TPS25730S part?