Hello team,

I need your help to know the right PMBUS programming sequence for this device.

I looked for the figure as the following example (not for TPS546D24A) on the TPS546D24A datasheet but couldn't find..

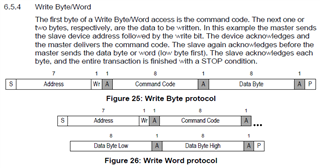

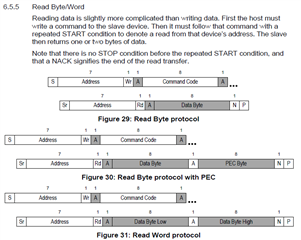

I had a trouble for both read and write after the Data to Register command. (Confirmed ACK in Slave Address and Command Byte comand.)

I guess that there is something of mismatch on the Data to Register format. Any of your kind advice is highly appreciated.

Thanks in advance.

S.Sawamoto