Other Parts Discussed in Thread: TUSB1046A-DCI, , TPS65981

Please tell me about the transfer speed of Type-c.

In our system, we connect the TPS65987D and TUSB1046AI in the same way as in "9.3 System Example" in the manual "tusb1046a-dci.pdf".

What we confirmed is that when an SSD (Solid State Drive) is connected directly with Type-c, the speed is very slow, about 35MByte/s, but when connected via a commercially available Type-c hub, the speed is 450MByte/s. .

When checking the following terminals on the board with an oscilloscope,

DP USB3 HPD FLIP

Not connected “L” “L” “L” “L”

Type-cHub connection “H” “H” “H” “H or L”

SSD direct connection “L” “L” “L” “H or L”

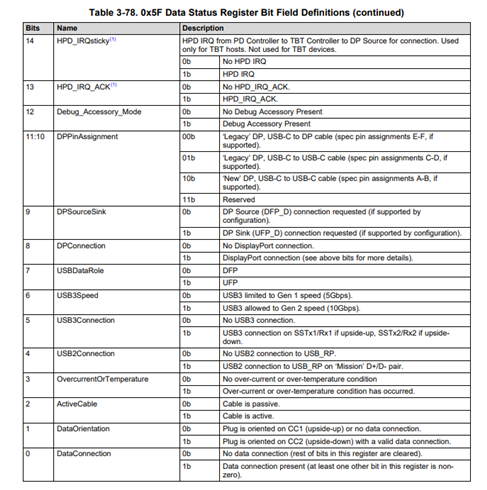

I assumed that if I directly connected the SSD, DP (CTL1) and USB3 (CTL0) would be at the "H" level and I expected the speed of USB3.0, but in reality, DP (CTL1) and USB3 (CTL0) were at the "L" level. Therefore, the speed will be USB 2.0.

Our hope is to connect directly to the SSD for high-speed data transfer, but this is currently not possible. Is there any possible reason?

Supplementary information

・SSD specifications are 1T Byte USB3.2 Gen 2×2 (USB 20Gbps).

・When you connect this SSD to a commercially available computer, you can transfer data at high speed.