Hi team,

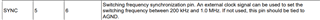

Is there any condition for applying external clock on SYNC pin?

For example, when external clock source is stopped, then resume applying clock, is there any concern?

It seems that datasheet doesn't mention any details for timing requirement of SYNC pin.

Best regards,

Shota Mago