Hello Experts,

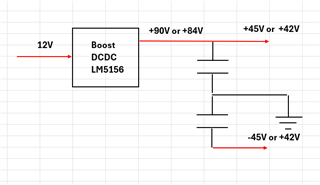

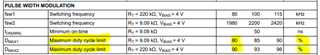

I create the desing to generate 90V using LM5156.

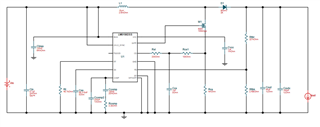

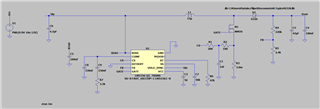

I use the same design from the WEBENCH

I took this design and simulated in the LTSpice.

For some reason the Vout is 22V for LTSpice, whereas in the WEBENCH is 89V.

Why is it happening? Do you know what is the issue?

Thank you,

Best,

Filipe S.