Other Parts Discussed in Thread: TPS25730,

USB Type C team,

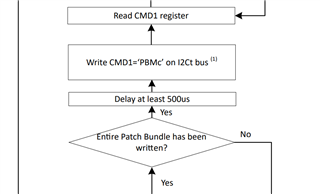

Our customer is using TPS25751 on the power Source side, and a TPS25730 on the Sink side. When configuring the TPS25751, they read the mode register and get PTCH, indicating they need to apply the patch update. They follow the steps in the flow chart in Figure 5-1 of the TRM. They get to the diamond in the bottom left where they expect to read DATA1=0 for success, but they always read 0x05.

Can you give advice on how to debug this so they can get to APP mode?

Thanks,

Darren