There was already a similar issue reported with the same title. We have faced out SW node short to AGND. What could cause this? Here are some design infos:

We are using the LM5122Z as a boost converter to provide ca. 66V at max. 0.8A (ca. 50W output power) for an input voltage range between 18-33V (typical) respectively 12 - 40V (emergency for some tens of seconds). The switching frequency is ca. 210kHz.

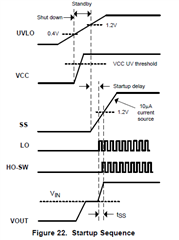

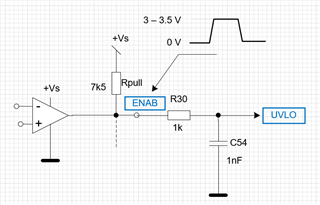

The fail occured at the following condition: input voltage raised to 51V, which triggers our own voltage monitor and disables the LM5122 via the UVLO pin (tie to low). During my observation the SW node fail occured if we reduced the voltage down to ca. 49V , which enables the LM5122 again. I obsereved strange acoustic noise from power components converter. After input power switch off we noticed the SW node short to AGND.

We have an input voltage transient limiter, which limits the input voltage to 53 - 54V in any case independend what the input transient is. So input voltage is well below any maximum ratings (e.g VIn or CSP SCN pin etc).

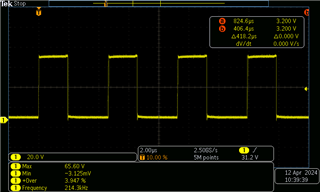

On another board with similar design we heave faced out no issues so far. I have also measured teh SW node via scope during this scenario - so captured first switching pulses at SW node after LM5122 re-enable (going below our own OVLO release threshold of ca. 49V). Is there a possibility that at some circumstances the input voltage is added onto the output voltage. From my understanding this behaviour is not expected for a boost converter., since the converter switch is on Low side.

I can double check with another board but would like to avoid to kill too many LM5122 with this kind of test. Therefore I would like to know theoretically the possible reason for the device fail.Therfore my dedicated questions.

Q1: How sensitive is the SW node to transients

Q2: what are the proper means to reduce transient overshoot at SW node w/o impacting efficiency.

-> I guess I will not have any issue with the -5V rating since the body diode of the low side MOSFET clamps to about -1V

Q3: is the damage on SW node only a side effect and caused by overvoltage to another pin

Regards Andreas