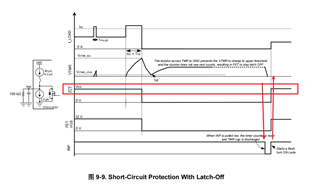

When we used the chip TPS12100, we found that in the short-circuit protection mode, according to the description in the data manual, the FLT fault can be cleared only when the INP input is first given to the low level and then to the high level, as shown in the following figure:

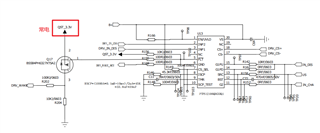

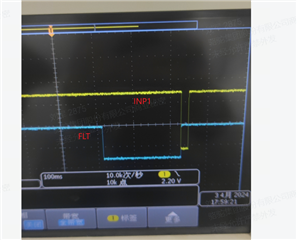

However, in the actual use process, it is found that when the short-circuit protection FLT becomes low, the MCU gives a low level to the INP, and the FLT fault state disappears immediately, as shown in the following figure. What is the reason for this? Is it the chip reason or the wrong way of use?