Hi,

The following E2E forums discuss FLT/SHDN. The forum answer states that "The device doesn't assert FLT when SHDN=LOW because it is not a fault scenario."

[Question]

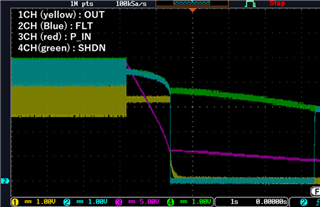

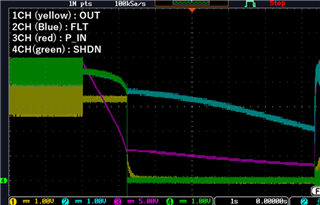

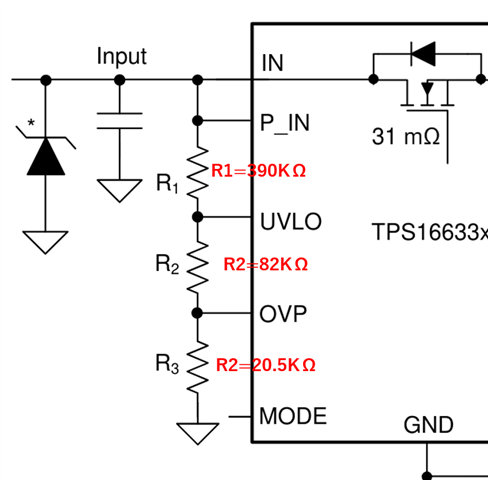

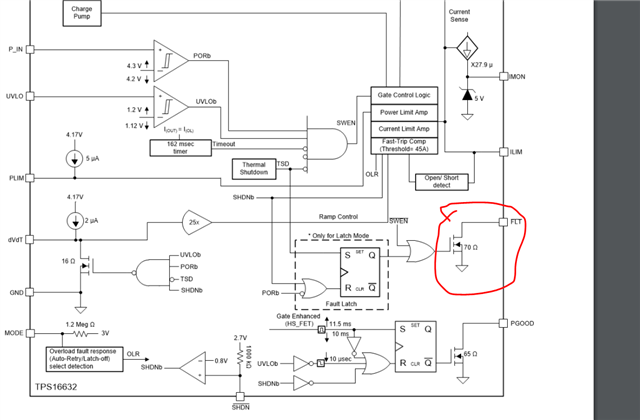

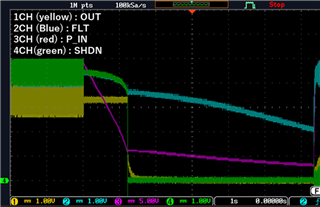

After the internal FET is turned off by the shutdown function, does UVLO work and FLT is asserted low?

Or when the device is turned off by the shutdown function, UVLO does not work and FLT is not asserted low?

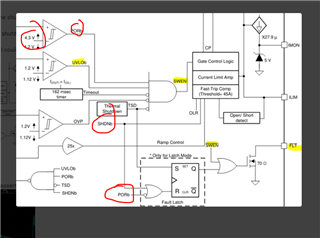

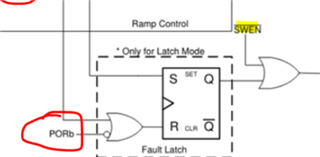

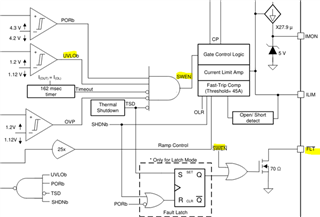

Looking at the internal block diagram, I couldn't find any circuit that relies on the shutdown function to determine whether FLT is asserted low.

Addendum

The customer wonders why FLT is not asserted low by ULVO after the internal FET is turned off by the shutdown function.

Best regards,

Conor