We are using UCC28950 in Slave mode.

Please tell me about the following.

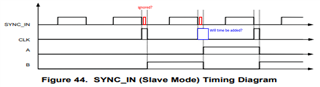

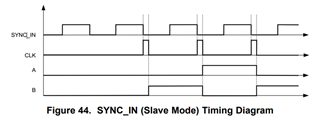

Q1.What is the time from the falling edge of SYNC to the falling edge of CLK.

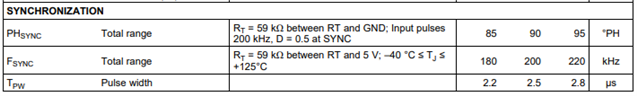

Q2.What is the falling threshold of SYNC to output CLK?

Q3.Please tell me what happens when SYNC falls when the CLK pulse is high.

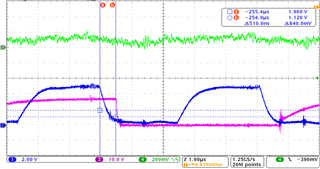

The OUTA and B outputs are becoming like double pulses due to noise to the SYNC terminal, and I would like information on how to take countermeasures.

Best regards.