Other Parts Discussed in Thread: TPS6594EVM, LP8764-Q1, TPS6594-Q1

Hi, TI expert

A customer has a question regarding the use of LP87644Q1EVM.

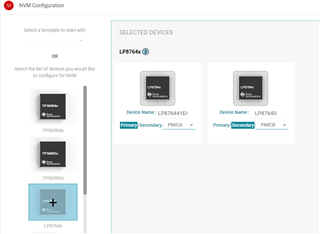

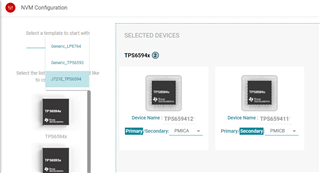

The customer is considering a System Power Management Interface (SPMI) related project (SPMI Master device development).

To verify SPMI functionality, we purchased 2 sets of PMIC_EVM Board (LP87644Q1EVM) to configure the test environment.

Customer have a few questions regarding this. For more information, please refer to the content and attached files below.

<Test purpose>

* Check SPMI Bus operation

: Verify the function of our SPMI device after configuring SPMI Bus by stacking PMIC EVB 1 (SPMI Master) - EVB 2 (SPMI Slave)

<Test environment>

* PMIC EVB 1, 2 : LP87644Q1EVM ( LP87644-Q1 evaluation module for four-output buck converter )

* Host PC

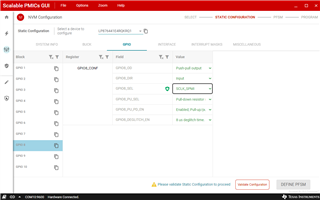

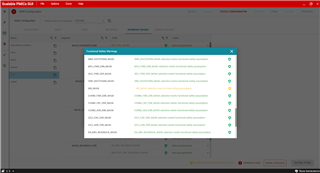

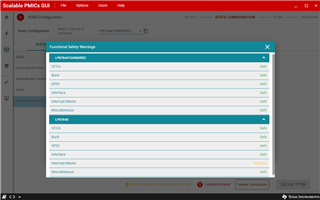

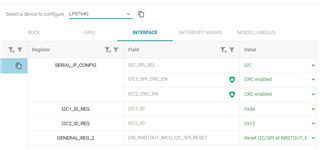

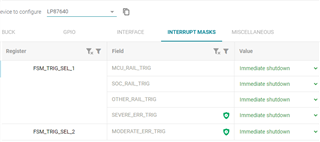

* PMIC EVB Test GUI S/W: Scalable-PMICs-GUI 3.0.0

<Test results>

* Connect PMIC EVB 1 and 2 to the Host PC respectively: Each Board is recognized by the PC

* Stacking PMIC EVB 1, 2 and connect to host PC: Only one board is recognized by PC

* SPMI Bus operation not confirmed.

[Question]

Q1) Is there anything incorrect in the test environment setting?

(According to the LP8764x-Q1 EVB User guide, it states that only power supply is required (Page_4))

Q2) Do you have any additional reference materials needed for review? If so, could you provide them?

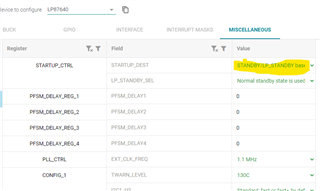

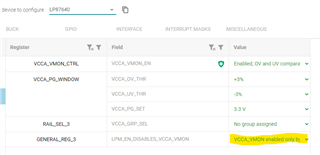

Q3) Do we need to modify the PMIC NVM (Non-volatile Memory) configuration for the test?

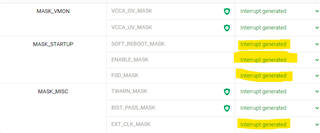

Ex) GPIO 8, 9 ( Multi-functional Pin. SPMI Clock, SPMI Data ) setting)

Currently, GPIO 8 and 9 are setting to default GPIO.

Ex) I tried to set SPMI Master and Slave ID, but I couldn't find the field setting function in the GUI.

Q4) Is there anything else I need to configure the test environment? ( ex. TPS6594EVM, etc. )

Please check. Thank you.

(related documents)

1. PMIC EVB ( LP87644Q1EVM ) Product Page: https://www.ti.com/tool/LP87644Q1EVM#supported-products

2. Test procedures and Question : HVS_SPMI_PMIC_EVB_test(Question Detail).pptx

(Question detail)_HVS_SPMI_PMIC_EVB_test.pptx

3. PMIC EVB User guide: LP87644Q1EVM.pdf

4. PMIC EVB Test GUI user guide: Scalable_PMIC_GUI_UserGuide.pdf

Scalable_PMIC_GUI_UserGuide.pdf

5. PMIC data sheet: LP8764-Q1.PDF