Other Parts Discussed in Thread: TPS541620,

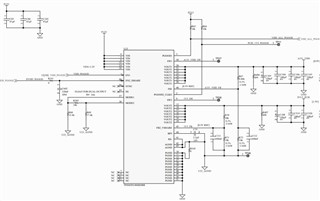

I am using the TPSM5D1806 in the following configuration:

VIN = 12V

VOUT1 = 0.9V (3A)

VOUT2 = 1.5V (2A)

1MHz switching frequency

500uF output capacitance on 0.9V rail.

300uF output capacitance on 1.5V rail.

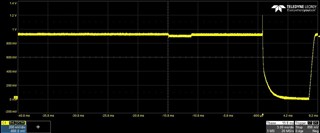

Both rails are stable during power up.

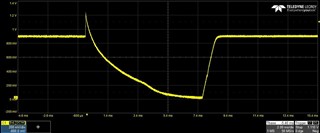

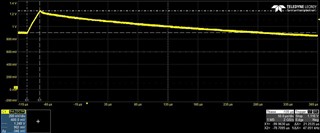

I am seeing the 0.9V rail spike (steady ramp from 0.9V toward 1.3V over 20ms) during current draw cycles (feeds the core voltage of a processor).

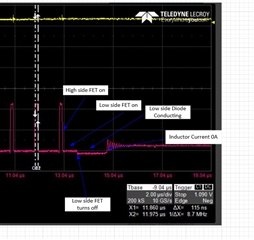

I monitor the SW1 pin and see pulses still going during this ramp (steadily decreasing in width). The the regulator turns off then on. My guess is the overvoltage on the output causes this.

What is going on here????? If the current draw were to suddenly go from 6A to 0A then I would expect a short increase in output voltage due to loop response. However, I would expect it to respond quicker than 20mS.

I tried feedforward caps in parallel to the upper feedback resistor (47pF, 150pF, 470pF) and there is never a change to the output.

I tried running the supply at 500kHz switching rate, no real change to behavior.

I added another 600uF of ceramic capacitance to the output, no change.

Any help will be much appreciated.

-Kevin