Respected sir,

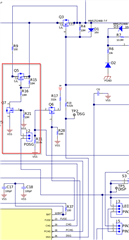

We are using TI BQ40Z80 IC in our design to design custom BMS battery pack having 6s configuration. We are using PDSG functionality in a BMS and Precharge could you please review our design and help us find out if there are any faults present it so we can rectify it before preceeding further. Below are the parameters on the basis of which we are designing our BMS:

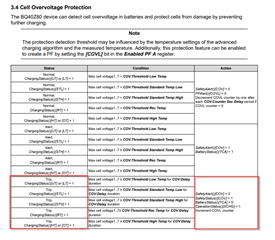

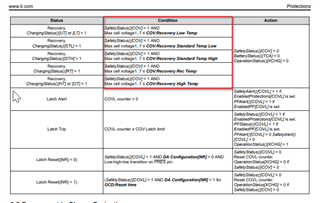

COV :4.2 V/cell

CUV : 2.5 V/cell

OCC: 2000 mA

OCD: 2500 mA

I have attached our design schematic and srec file for your reference, please have a look on it. I also want to know apart from BQ40Z80 is there any other BQ chip available for 6s configuration which can fulfill our requirements stated above.

Regards;

Shubham

4544.BMS.pdfBMS NEW srec.zip

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.