hi TI team

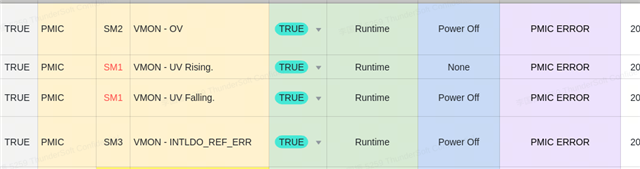

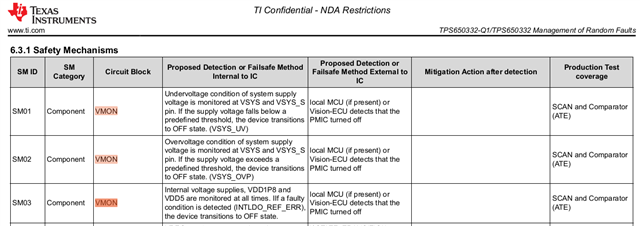

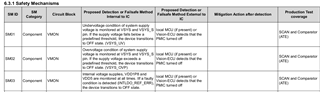

As for the fault detection items of the TPS650332-Q1 chip, according to the fault detection items of SM1 to SM3 as shown in the following figure, the document mentions the local MCU(if there is one) or Vision-ECU detects PMIC shutdown, which conditions should be met for detection here.

Can it be understood that external hardware is required to detect the voltage value?