Other Parts Discussed in Thread: TPS22965

Hi Team ,

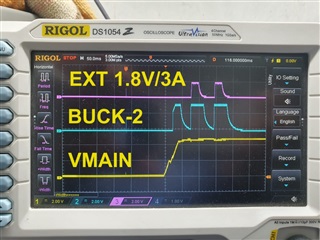

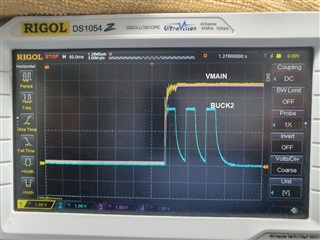

We are using PMIC TPS6521901 for powering AM6442BSEFHAALV . We are in the board bring up stage but struck with the PMIC powering up . We are using 5V input and the enable pin is tied to 5V. but PMIC is not responding . TPS6521901_pmic_Arm64x.pdf

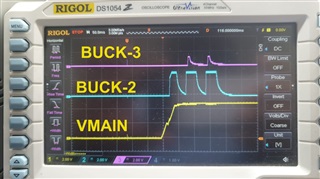

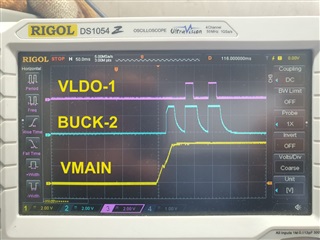

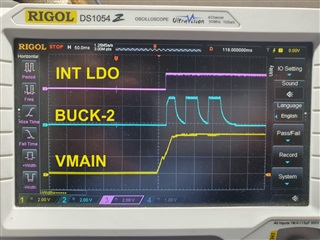

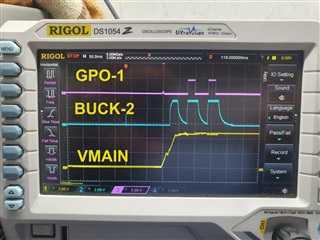

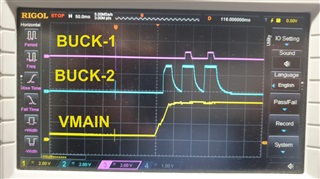

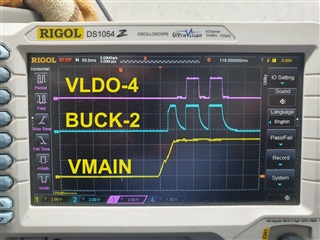

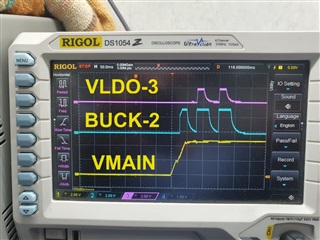

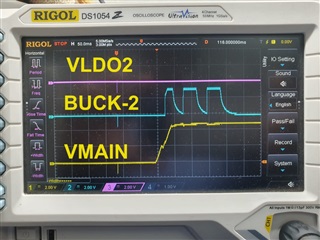

Please see the attached schematics used .  . We tried to isolate the output rails by disconnecting the zero ohms in the o/p rails

. We tried to isolate the output rails by disconnecting the zero ohms in the o/p rails

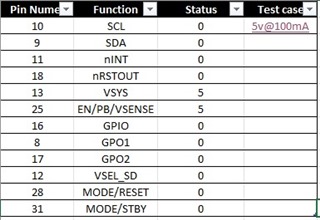

The voltages measured at each control pin is also listed . Kindly go through the schematics and share some lights .

What shall be the minimum current from the input supply to start functioning the device ? The input current is measured as 4 mA only now .

The source current is limited to 500mA for the test purpose (no load is connected)