Other Parts Discussed in Thread: CSD87381P, TPS650861

Hi

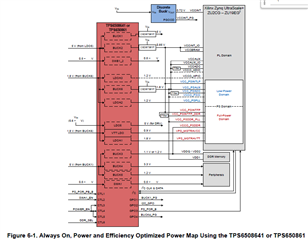

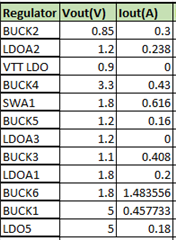

We are designing our Video Processing board using Xilinx Ultrascale FPGA XCZU3CG-L1SFVC784I.We are designing for low power.

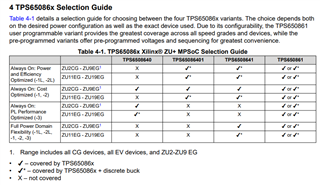

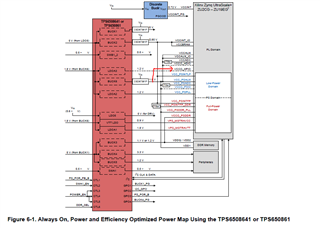

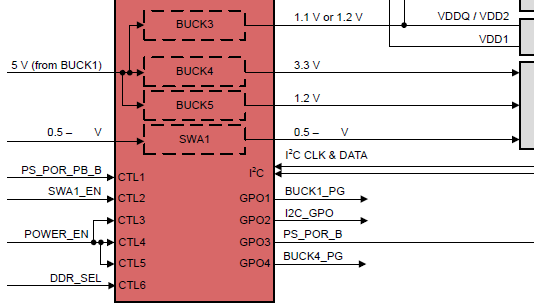

We are planning to use TPS6508641 to power this.

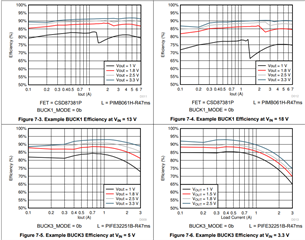

- We want to do thermal analysis to check if junction temperature is within limit. Please let me know if there is any calculator for this.

- Any heat sink would be required?

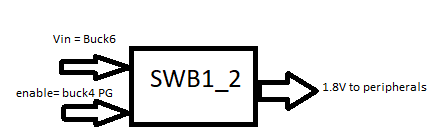

- There is no 3.3V from PMIC connected to the FPGA in the implementation in doc SCEA113, sec 6.1. How to interface FPGA with peripherals which are operating at 3.3V?