Hi Team,

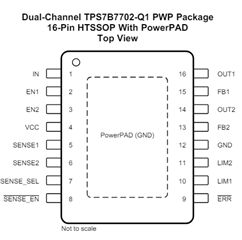

We are using the TPS7B7702-Q1, we are very care about the Rja data, the application is the automotive. So we plan to design a resistance test board to double-confirm the Rja data just like datasheet said, to make sure and select the qualified device, Rja should be about 40.3℃/W.

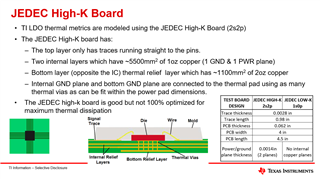

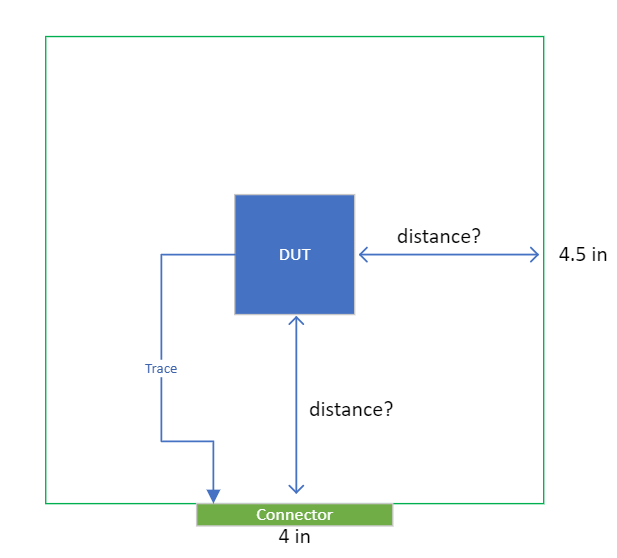

But we don't have the detailed requirement for the below JEDEC standard, and if you can share it to us or show the reference Rja test board, will be appreciate, thanks in advance.

Best Regards,

Kunyue