Respected TI experts

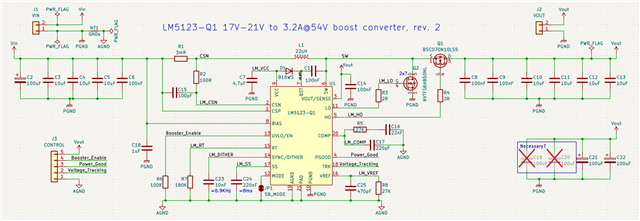

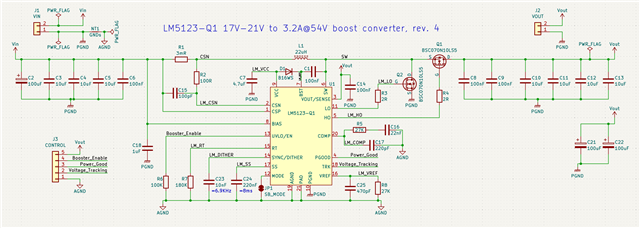

I kindly ask you to review the component selection and the layout of this boost converter design.

For context: this is an LED driver working up from a 5S2P li-ion battery pack. (Current) regulation is done via the tracking input with an external MCU and current sense resistor. There is also an external low-side switch to quickly turn the LED on or off (strobe functionality).

The converter is intended to be functional with full power output of 3.2A@54V at 17.5V minimum input.

To minimize switching losses in this thermally challenged application (there is only a little airflow from a nearby cooling fan), a relatively low switching frequency of about 120KHz was selected.

Because the inductor would otherwise be huge, expensive and poorly available, a high ripple current ratio of about 60% had to be chosen. I accept the resulting higher core loss and lower light load efficiency (earlier DCM).

The PCB is a 6-layer board with plated-over filled vias and 1-0.5-0.5-0.5-0.5-1 oz copper thickness. 6 layers are used because they are needed for other parts of the application.

My primary concerns are:

- Do you advise against using a current sense resistor value smaller than recommended by the quickstart calculator? As I see it, it will reduce losses and low frequency gain. The current limit would also be too high, but that is already taken care of by the battery protection circuitry. Would 2mΩ or even 1mΩ be fine too?

- Is the QH-QL-COUT loop small enough? Does it need more small output capacitors? Currently there are two 0805 100nF X7R output capacitors directly besides QH and one near the device.

- The RS-LM-CIN loop is not as critical (less di/dt) but is it fine too?

- Is SW/HO/Vout routed directly enough? The "accessory" capacitors are somewhat in the way, but I'd like to not have to use smaller packages with poor DC bias characteristics.

- Is LO/GNDPWR routed directly enough? LO is wide and runs on the GNDPWR plane but has vias in the way.

- I surrounded the rather long current sense tracks with GNDA zones above and below. Is this a bad idea?

- The SW pour is on the smaller side. I believe that the massive copper wire of the inductor will sink away some of the heat and a large noisy plane for heat dissipation is therefore not necessary.

EDIT: All attachments have been removed from this question as they were reported to be missing!

Thank you very much in advance,

Adrian